# Providing a Formal Linkage between MDG and HOL Based on a Verified MDG System

A thesis submitted to Middlesex University in partial fulfilment of the requirement for the degree of Doctor of Philosophy

Haiyan Xiong

School of Computing Science

Middlesex University

January 2002

#### Abstract

Formal verification techniques can be classified into two categories: deductive theorem proving and symbolic state enumeration. Each method has complementary advantages and disadvantages. In general, theorem provers are high reliability systems. They can be applied to the expressive formalisms that are capable of modeling complex designs such as processors. However, theorem provers use a glass-box approach. To complete a verification, it is necessary to understand the internal structure in detail. The learning curve is very steep and modeling and verifying a system is very time-consuming. In contrast, symbolic state enumeration tools use a black-box approach. When verifying a design, the user does not need to understand its internal structure. Their advantages are their speed and ease of use. But they can only be used to prove relatively simple designs and the system security is much lower than the theorem proving system. Many hybrid tools have been developed to reap the benefits of both theorem proving systems and symbolic state enumeration systems. Normally, the verification results from one system are translated to another system. In other words, there is a linkage between the two systems. However, how can we ensure that this linkage can be trusted? How can we ensure the verification system itself is correct?

The contribution of this thesis is that we have produced a methodology which can provide a formal linkage between a symbolic state enumeration system and a theorem proving system based on a verified symbolic state enumeration system. The methodology has been partly realized in two simplified versions of the MDG system (a symbolic state enumeration system) and the HOL system (a theorem proving system) which involves the following three steps. First, we have verified aspects of correctness of two simplified versions of the MDG system. We have made certain that the semantics of a program is preserved in those of its translated form. Secondly, we have provided a formal linkage between the MDG system and the HOL system based on importing theorems. The MDG verification results can be formally imported into HOL to form the HOL theorems. Thirdly, we have combined the translator correctness theorems with the importing theorems. This combination allows the low level MDG verification results to be imported into HOL in terms of the semantics of a high level language (MDG-HDL). We have also summarized a general method which is used to prove the existential theorem for the specification and implementation of the design. The feasibility of this approach has been demonstrated in a case study: the verification of the correctness and usability theorems of a vending machine.

## Acknowledgments

I have been very fortunate to have had Dr. Paul Curzon, Prof. Ann Blandford and Prof. Sofiène Tahar as my supervisors. I am deeply grateful for their support and encouragement throughout my Ph.D studies. I am most indebted to them for the considerable amount of time they each devoted to me in my research work. I extend my deepest thanks especially to Dr. Paul Curzon, without whose invaluable guidance I could not have completed this work.

In this thesis, several of the chapters are based on publications that were produced in the course of this research. The papers published jointly with my supervisors were all first-authored by me, and all report on my own work, completed under their supervision [78 - 83]. The work reported in Chapter 5 realized a general idea of Curzon and Tahar [80]: I formalized that idea in HOL. The work reported in Chapter 8 takes an example that was originally developed by Curzon and Blandford [24], and applies the approach developed within this thesis to that same example. The MDG verification was completed with the help of Tahar. All the HOL proof is my own work, again completed under their supervision.

I would like to thank people in the Automated Reasoning Group in Cambridge and the MDG group in Montreal, Prof. Mike Gordon, Dr. Konrad Slind, Dr. Michael Norrish, Joe Hurd, Dr. Richard Boulton and Prof. Tom Melham. When I have needed help they have always lent me a hand. I have benefitted so very much

from their vast knowledge and insight.

I am particularly thankful to Dr. Wai Wong, who not only introduced me to this field, but also provided a great deal of assistance.

Many thanks to Sardia, who provided fabulous administrative support, and to Leonard, who was always available whenever I had problems with my computer.

I would like to reserve my deepest thanks for my parents for their perpetual love and encouragement, and to my husband and my son for their sacrifices and patience. I can never thank them enough.

Lastly, I would like to acknowledge the support obtained from the School of Computing Science, Middlesex University and EPSRC grant GR/M45221.

#### Haiyan Xiong

## Contents

| A | bstra | ıct    |                                                                           | ii |

|---|-------|--------|---------------------------------------------------------------------------|----|

| A | ckno  | wledgr | nents                                                                     | iv |

| 1 | Intr  | oducti | ion                                                                       | 1  |

|   | 1.1   | The M  | IDG System                                                                | 5  |

|   | 1.2   | The H  | IOL System                                                                | 7  |

|   | 1.3   | Overv  | view of the Research                                                      | 8  |

|   |       | 1.3.1  | Verifying the MDG Translators                                             | 10 |

|   |       | 1.3.2  | The Importing Theorems                                                    | 16 |

|   |       | 1.3.3  | Combining the Translator Correctness Theorems with the Importing Theorems | 18 |

|   |       | 1.3.4  | Proving the Existential Theorem                                           | 21 |

|   | 1 4   | Outlir | ne of Thesis                                                              | 22 |

| 2 | $\operatorname{Lit}\epsilon$ | erature Review                                                                   | 26 |

|---|------------------------------|----------------------------------------------------------------------------------|----|

|   | 2.1                          | Semantic Embedding                                                               | 27 |

|   | 2.2                          | Verifying Verification Systems                                                   | 29 |

|   | 2.3                          | Verifying Compiler Correctness                                                   | 32 |

|   | 2.4                          | Trusting Combined Systems                                                        | 35 |

| 3 | Ver                          | ifying the MDG Translators for a Boolean Subset                                  | 42 |

|   | 3.1                          | The Syntax of the MDG-HDL Language                                               | 43 |

|   | 3.2                          | The Syntax of the Core MDG-HDL Language                                          | 48 |

|   | 3.3                          | The Syntax of the MDG Formula Representation Program                             | 48 |

|   | 3.4                          | Translating MDG-HDL into the Core MDG-HDL Language                               | 50 |

|   | 3.5                          | Translating the Core MDG-HDL Program into the MDG Formula Representation Program | 52 |

|   | 3.6                          | The Semantics of the MDG-HDL Program                                             | 56 |

|   | 3.7                          | The Semantics of the Core MDG-HDL Program                                        | 63 |

|   | 3.8                          | The Semantics of the MDG Formula Representation Program                          | 64 |

|   | 3.9                          | Translator Correctness Theorems                                                  | 66 |

| 4 | Ver                          | ifying the MDG Translator for the Extended Subset                                | 70 |

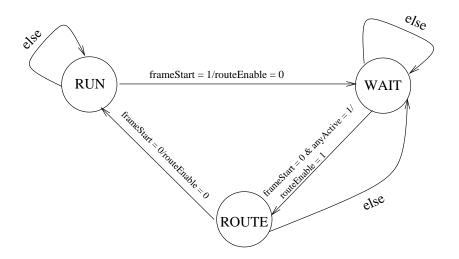

|   | 4.1                          | State Transitions of the Fairisle Switch Fabric Timing Block                     | 71 |

|   | 4.2 | The Syntax of the MDG-HDL Language                                                              | 73  |

|---|-----|-------------------------------------------------------------------------------------------------|-----|

|   | 4.3 | The Syntax of the Core MDG-HDL Language                                                         | 75  |

|   | 4.4 | Compiling MDG-HDL into the Core MDG-HDL Language                                                | 76  |

|   | 4.5 | The Semantics of the MDG-HDL Program                                                            | 77  |

|   | 4.6 | The Semantics of the Core MDG-HDL language                                                      | 85  |

|   | 4.7 | Translator Correctness Theorem                                                                  | 87  |

| 5 | Im  | porting Theorems                                                                                | 89  |

|   | 5.1 | Combinational Verification                                                                      | 92  |

|   | 5.2 | Sequential Verification                                                                         | 92  |

|   | 5.3 | Invariant Checking                                                                              | 96  |

| 6 |     | nbining the Compiler Correctness Theorems with the Importing eorems                             | 99  |

|   | 6.1 | Combining the Translator Correctness Theorems with the Importing Theorems for a Boolean Subset  | 102 |

|   |     | 6.1.1 Combinational Verification                                                                | 102 |

|   |     | 6.1.2 Sequential Verification                                                                   | 105 |

|   | 6.2 | Combining the Translator Correctness Theorem with the Importing Theorems for an Extended Subset | 111 |

|   |     | 6.2.1 Combinational Verification                                                                | 111 |

|   |     | 6.2.2 Sequential Verification                                                          | 112      |

|---|-----|----------------------------------------------------------------------------------------|----------|

| 7 | Exi | stential Theorems                                                                      | 115      |

|   | 7.1 | Existential Theorem for the Extended Subset                                            | 118      |

|   | 7.2 | The Output Representation for the Basic MDG-HDL Components                             | 119      |

|   | 7.3 | The Output Representation for TABLE Components                                         | 121      |

|   | 7.4 | Dealing with the Existential Quantified Internal Variables                             | 126      |

|   | 7.5 | An Example                                                                             | 127      |

| 8 |     | e Study: Verification of the Correctness and Usability Theo<br>as of a Vending Machine | -<br>131 |

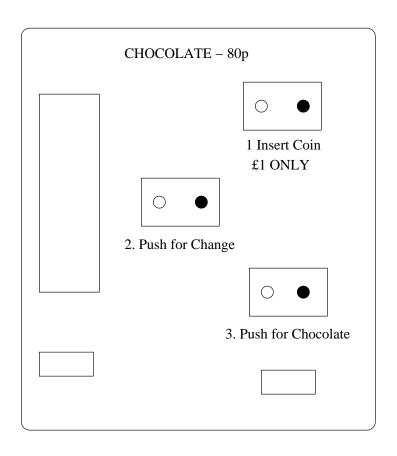

|   | 8.1 | Chocolate Machine                                                                      | 134      |

|   | 8.2 | Proving the Chocolate Machine using the MDG System                                     | 134      |

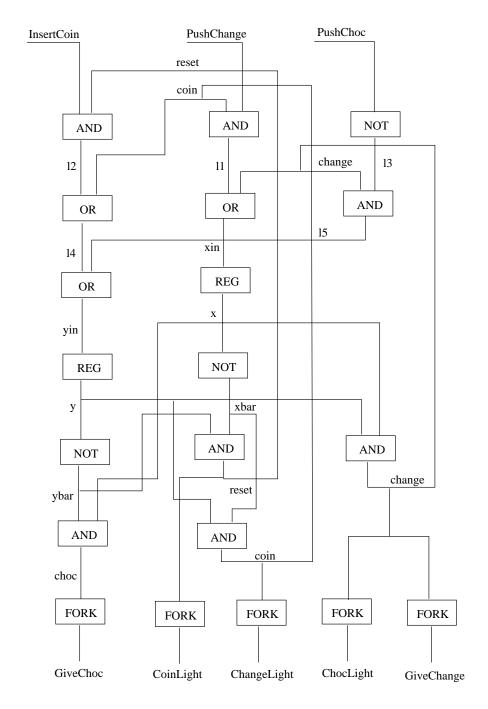

|   |     | 8.2.1 The Implementation                                                               | 136      |

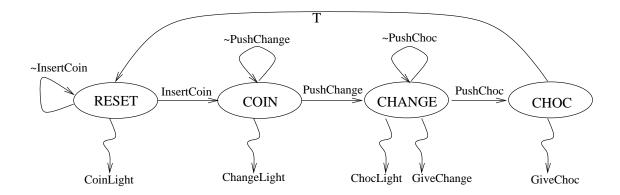

|   |     | 8.2.2 The Specification                                                                | 139      |

|   |     | 8.2.3 Three Other Specification Files                                                  | 141      |

|   | 8.3 | The Importation Process of the Verification Results                                    | 141      |

|   |     | 8.3.1 The Syntax and the Semantics of the Chocolate Machine                            | 142      |

|   |     | 8.3.2 Importing the MDG Results into HOL                                               | 146      |

|   | 8.4 | Verification of the Usability Theorems                                                 | 151      |

| 9            | Conclusions and Future Work |                                                          |              |

|--------------|-----------------------------|----------------------------------------------------------|--------------|

|              | 9.1                         | Conclusions                                              | 156          |

|              | 9.2                         | Future work                                              | 161          |

| A            | The                         | Abstract Syntax of a Boolean Subset                      | 174          |

| В            | The                         | Abstract Syntax of an Extended Subset                    | 177          |

| $\mathbf{C}$ | The                         | MDG-HDL programs of the verification of the Chocolate Ma | <del>-</del> |

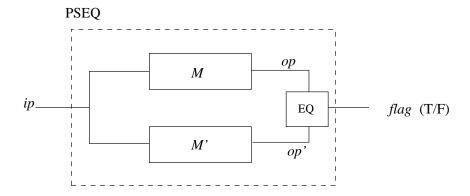

|              | chin                        | e                                                        | 180          |

## List of Figures

| 1.1 | Overview of the Research                                           | S  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | The AND Table                                                      | 11 |

| 1.3 | Overview of the MDG Translation Phases                             | 11 |

| 1.4 | The AND Gate in the MDG Formula Representation                     | 12 |

| 1.5 | The MDG Translation Phases                                         | 12 |

| 1.6 | Compilation Correctness                                            | 14 |

| 1.7 | Hierarchical Verification                                          | 17 |

| 1.8 | The MDG Verification Process                                       | 20 |

| 2.1 | The MDG Verification System                                        | 32 |

| 3.1 | The Circuit Description File of Three NOT Gates and One Register . | 44 |

| 3.2 | The Syntax of a NOT Gate Table                                     | 46 |

| 3.3 | The Abstract Syntax of a Core MDG-HDL Program                      | 49 |

| 3.4 | The Syntax of an AND Gate Table                                                              |

|-----|----------------------------------------------------------------------------------------------|

| 3.5 | Translating the MDG-HDL program into the Core MDG-HDL program 5                              |

| 4.1 | State Transitions of the Fairisle Switch Fabric Timing Block 7                               |

| 4.2 | The Behavior of the Fairisle Switch Fabric Timing Block                                      |

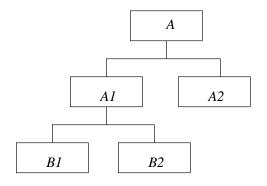

| 5.1 | The Hierarchy of Module $A$                                                                  |

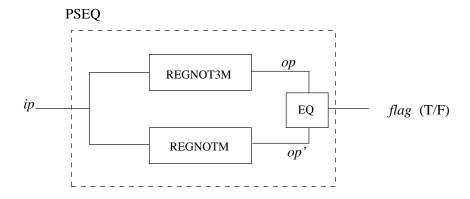

| 5.2 | The Product Machine used in MDG Sequential Verification 9                                    |

| 5.3 | The Machine Verified in Invariant Checking                                                   |

| 6.1 | Combining the Translator Correctness Theorems with Importing Theorems for a Boolean Subset   |

| 6.2 | Combining the Translator Correctness Theorems with Importing Theorems for an Extended Subset |

| 6.3 | Two Equivalent Combinational Circuits                                                        |

| 6.4 | The Machine used for Sequential Verification of the REGNOT3M  Circuit                        |

| 7.1 | The Output of a TABLE is a State Variable and Contains in the Input list                     |

| 7.2 | A Circuit                                                                                    |

| Q 1 | The Chocolate Machine                                                                        |

| 8.2 | The Circuit of the Chocolate Machine                                      |

|-----|---------------------------------------------------------------------------|

| 8.3 | The State Transition Diagram of the Chocolate Machine 139                 |

| 8.4 | The Abstract Syntax of the Specification File                             |

| 8.5 | The Abstract Syntax of the Implementation File                            |

| 8.6 | The Semantics of the Specification File                                   |

| 8.7 | The Existential Theorem of the Specification of the Chocolate Machine 149 |

### Chapter 1

#### Introduction

Formal methods are the application of applied mathematics - formal logic - to the design and analysis of computer systems. Generally, formal verification techniques can be classified into two categories: deductive theorem proving and symbolic state enumeration. In deductive theorem proving systems, the correctness condition for a design is represented as a theorem in a mathematical logic, and a mechanically checked proof of this theorem is generated using a general-purpose theorem prover. In symbolic state enumeration systems, the design being verified is represented as a decision diagram. Techniques such as reachability analysis are used to automatically verify given properties of the design or machine equivalence. Much of this work is based on Binary Decision Diagrams (BDD) [4] [11].

Deductive theorem proving systems use interactive proof methods. In these systems, an implementation and its behavioral specification are represented as first-order or higher-order logic formulas. The user interactively constructs a formal proof which proves a theorem stating the correctness of this implementation. Theorem proving systems are naturally deductive process systems. They allow a hierarchical verification method to be used to model the overall functionality of designs with complex datapaths. They are very general in their applications. The theorems can

not only be used to formalize a specific design but also can be abstracted as a general situation of this class of design. Theorem proving systems are semi-automated. To complete a verification, experts with good knowledge of the internal structure of the design are required to guide the proof searching process. This enables the designer to gain greater insight into the system and thus achieve better designs. However, the learning curve is very steep, modelling and verifying a system is very time-consuming. This is the major difficulty to applying the theorem proving systems in industry.

In contrast, symbolic state enumeration systems are automated decision diagram approaches. In this kind of approach, an implementation and its behavioral specification are represented as decision diagrams. A set of algorithms is used to efficiently manipulate the decision diagrams so as to get the correctness results. The introduction to the BDD based method by Hu [47] may be taken as a good reference. In contrast to the theorem prover, symbolic state enumeration verification is a relatively modest activity. It normally deals with a single model rather than the whole design. The symbolic state enumeration verification approach can be viewed as a black-box approach. During the verification, the user does not need to understand the internal structure of the design. The strength of this approach is its speed and ease of use. However, it does not scale well to complex designs since it uses non-hierarchy state-based descriptions of the design. An increase in the number of design components can result in the state space growing exponentially.

In the 1990s, the efficiency breakthrough in symbolic state enumeration was such that industry has successfully applied symbolic state enumeration tools in digital circuit synthesis and verification. Since then, more and more tools have been developed including Spin [45], MDG [20], STE [72] and so on. Although they have been very successfully used in industry, there are still many deficiencies in the currently available symbolic state enumeration tools. Although the symbolic state enumeration based tools can be applicable to circuits of considerable size, they still do not scale up sufficiently. However, the theorem proving systems can be applied to large

designs in theory, although in practice it is time consuming. One solution is to combine these two kind of systems to reap the advantages of both. This combination allows the fully automated proof tools to rely on a theorem proving system and the increasing size and complexity of a design can be handled in practice.

Recently, there has been a great deal of work concerned with combining the theorem proving and symbolic state enumeration systems. A common approach to combining proof tools is to use an symbolic state enumeration system as an oracle to provide results to the theorem proving system. The issue in such work is to guarantee that the results provided by external tools are theorems within the theory of the proof system. In other words, an oracle is used to receive problems and return answers. For example, the HOL system provides approaches for tagging theorems that are dependent on the correctness of external verification tools. An oracle can be built in the HOL system is viewed as a plug-in. This brings about two questions.

- 1. Can we ensure the automated verification system produces the correct results?

- 2. Have the verification results from an automated verification system been correctly converted into a valid theorem in the current theory of the theorem proving system?

The research describe here investigates the answers to the above two questions. In fact, some symbolic state enumeration based systems such as MDG [20] consist of a series of translators and a set of algorithms. Higher level languages such as hardware description languages are used to describe the specification and implementation of the design. The specification and implementation are then translated into the decision diagrams via intermediate languages. The algorithms in the system are used to efficiently and automatically deal with the decision diagrams so as to obtain the correctness results. We need to verify the translators and algorithms in order to get the answer of the first question. For solving the second question, we need to formally justify the correctness results, which are obtained from a symbolic

state enumeration system, into a theorem prover, to ensure the correctness of the theorem creation process.

In this thesis, we will produce a methodology, which can provide a formal linkage between a theorem proving system and a symbolic state enumeration system based on a verified symbolic state enumeration system, to ensure the correctness of the theorem creation process. We first need to verify aspects of correctness of the symbolic state enumeration system in an interactive theorem proving system. We then need to prove the translators and algorithms to ensure the correctness of the system. By combining the translator correctness theorems with the importing theorems, the verification results from the state enumeration system can be imported into the theorem proving system in terms of the semantics of high level language (HDL) rather than low level language (decision graph). We also need to summarize a general method to prove the existential theorem of the design, which is needed for importing sequential verification result into the theorem proving system.

We will partly realize the methodology in the HOL system and two simplified versions of the MDG system. We will prove the correctness of aspects of the simplified versions of the MDG system and provide a formal linkage between the HOL system and the simplified versions of the MDG system. Lessons from the research could be applicable to other related systems. We chose HOL and MDG because this research is part of a large project in collaboration with the Hardware Verification group at Concordia University. They are developing a hybrid system (MDG-HOL) [54] [53] [66] which combines the MDG system and the HOL system. Our aim is different to theirs. We are not developing a practical tool. We are doing theoretical research about how to verify the MDG system and provide a formal linkage between the HOL system and the MDG system. Our deep embedding semantics is in terms of the specification of the MDG system. Since we will consider the simplified versions of the MDG system, in the rest of this thesis, we will refer to the simplified versions of the MDG system as 'the MDG system' except in the section 1.1.

In the research, we first consider verifying the translation phases of the MDG system using the HOL system and obtain a series of correctness theorems. By combining those theorems, we obtain that the semantics of a low level MDG program equals the semantics of a high level MDG-HDL program (the MDG input language). We then consider how to formally import the MDG verification results to a form that can be used in the HOL system. We formalize the MDG verification results in terms of the semantics of the low level MDG program and turn them into HOL to form the HOL theorems. By combining the translation correctness theorems with the importing theorems, we obtain theorems which convert the low level MDG verification results into HOL to form the HOL theorem based on the semantics of the MDG input language. In other words, this combination allows the imported theorem to be in terms of the semantics of the MDG-HDL. For easily importing the MDG results into HOL for sequential verification, we summarize a general way to prove the existential theorem (a theorem which has form:  $\forall$  ip.  $\exists$  op.  $\Diamond$  ip op). All the theorems in this thesis written with  $\vdash_{thm}$  have been proved in HOL.

The structure of the rest of this chapter is as follows: In sections 1.1 and 1.2, we will briefly introduce the MDG system and the HOL system respectively. An overview of the research will be given in section 1.3. Finally, an outline of this thesis will be presented in the last section.

#### 1.1 The MDG System

The full MDG system is an automated verification tool for hardware verification. It uses a new class of decision graphs called Multiway Decision Graphs, which subsume the class of Bryant's Reduced and Ordered Binary Decision Diagrams (ROBDD) [12] while accommodating abstract sorts and uninterpreted function symbols.

A multiway decision graph (MDG) is a finite directed acyclic graph G where the leaf nodes are labeled by formulas, the internal nodes are labeled by terms and the

edges issuing from an internal node, N, are labeled by terms of the same sort as the label of N. Such a graph represents a formula defined inductively as follows:

- 1. If G consists of a single leaf node labeled by a formula P, then G represents P,

- 2. If G has a root node labeled A with edges labeled  $B_1...B_n$  leading to subgraphs  $G_1'...G_n'$ , and if each  $G_i'$  represents a formula  $P_i$ , then G represents the formula  $\bigvee_{1 \le i \le n} ((A = B_i) \land P_i)$ .

In fact, when an MDG has been constructed as a graph, it must obey the restrictions that any path from the root to leaf yields a canonical representation. Like ROBDDs, an MDG must be reduced and ordered. Unlike ROBDDs, all the variables used in an MDG must have appropriate sort, and sort definitions must be provided for all functions. MDG can also represent the transition and output relations of a state machine, as well as the set of possible initial states and the sets of states that arise during reachability analysis.

The underlying logic of MDG is a subset of many-sorted first-order logic with a distinction between concrete and abstract sorts. A concrete sort has an enumeration while an abstract sort does not. Therefore, a data signal can be represented by a single variable of abstract sort and a data operation can be represented by an uninterpreted function symbol. It partially fulfills the aim of interactive verification to verify hardware designs automatically at a high level of abstraction. It also lifts many ROBDD techniques from the boolean domain to a more abstract domain. In particular, a data signal in an MDG is represented by a single variable of abstract sort rather than a vector of boolean variables, and the data represents an operation by an uninterpreted function symbol. Therefore, MDGs are more compact than ROBDDs for circuits having a datapath, and this greatly increases the range of circuit that can be proved.

The MDG package has been implemented in Prolog. Algorithms such as disjunction, relational product (combination of conjunction and existential quantification),

pruning-by-subsumption (for testing of set inclusion) and reachability analysis (using abstract implicit enumeration) have been developed. Applications for hardware verification such as combinational verification, sequential verification, invariant checking and model checking are provided.

#### 1.2 The HOL System

The HOL system is an LCF (Logic of Computable Functions) style proof system. It uses higher-order logic to model and verify a system. There are two main different proof methods: forward and backward proof. In forward proof, the steps of a proof are implemented by applying inference rules chosen by the user, and HOL checks that the steps are safe. All derived inference rules are built on top of a small number of primitive inference rules. In backward proof, the user sets the desired theorem as a goal. Small programs written in SML [65] called tactics and tacticals are applied to breaking the goal into a list of subgoals. Tactics and tacticals are repeatedly applied to the subgoals until they can be resolved. A justification function is also created mapping a list of theorems corresponding to subgoals to a theorem that solves the goal. In practice, forward proof is often used within backward proof to convert each goal's assumptions to a suitable form.

Theorems in the HOL system are represented by values of the ML abstract type thm. There is no way to construct a theorem except by carrying out a proof based on the primitive inference rules and axioms. More complex inference rules and tactics must ultimately call a series of primitive rules to do the work. In this way, the ML type system protects the HOL logic from the arbitrary construction of a theorem, so that every computed value of the type-representing theorem is a theorem. The user can have a great deal of confidence in the results of the system.

HOL has a rudimentary library facility which enable theories to be shared. This provides a file structure and documentation format for self contained HOL devel-

opments. Many basic reasoners are given as libraries such as mesonLib, simpLib, decisionLib and bossLib. These libraries integrate rewriting, conversion and decision procedures that automate a proof. They free the user from performing low-level proof.

#### 1.3 Overview of the Research

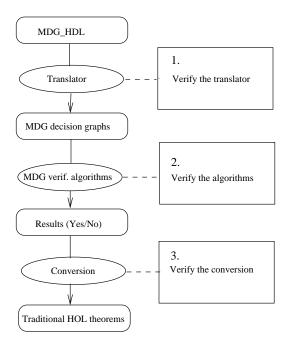

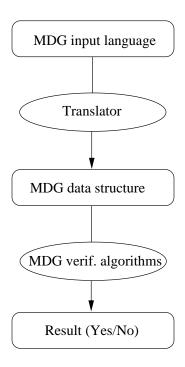

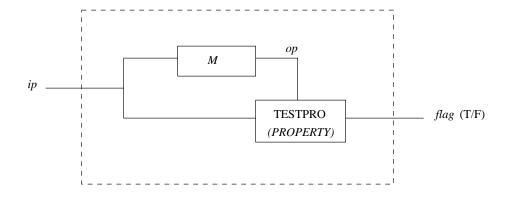

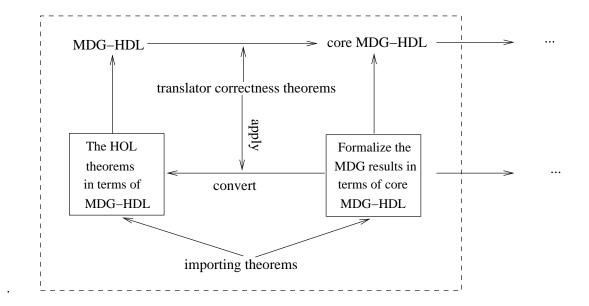

The intention of our research is to explore a way of increasing the degree of trust of the MDG system and provide a formal linkage between the HOL system and the MDG system as shown in Figure 1.1. This work can be divided into three steps. (a) We must verify the correctness of the MDG system using the HOL system. It consists of two phases—(1) verification of the translators [82] and (2) verification of the algorithms. (b) We then must prove theorems (step 3 in Figure 1.1), which formally convert the verification results of different MDG applications into the traditional HOL hardware verification theorems [80]. (c) By combining the correctness theorems (theorems obtain from step 1, 2 in Figure 1.1) of the verification of the MDG system with the importing theorems (theorems obtain from step 3 in Figure 1.1), the MDG verification results can be imported into HOL in terms of the MDG input language.

During this study, we concentrate on the verification of the translation phase of the MDG system (step 1, Figure 1.1) using the HOL theorem prover and importing the MDG results into HOL to form the HOL theorems (step 3, Figure 1.1) [80]. Step 2 is similar to Chou and Peled's work [17] which verifies a partial-order reduction technique for model checking. Verifying the algorithms is beyond the scope of this thesis, as we are primarily concerned with the linkage and how it could be combined with the correctness theorems and importing theorems. We outline the methodology of the whole story and emphasize the importation process of the hybrid system. We not only verify the correctness of aspects of the MDG system in HOL, but also formally import the MDG results into HOL to form the HOL theorems based on the

Figure 1.1: Overview of the Research

semantics of the high level MDG input language (MDG-HDL) [86] rather than the semantics of the low level language. Since we use a deep embedding semantics, the translator correctness theorems can be combined with other translator correctness theorems and the importing theorems. These combinations allow the low level MDG results to be converted into a form that can be easily reasoned about in HOL based on the semantics of MDG-HDL. We also summarize the general method about proving the existential theorem to remove the burden from the user of the combined system. This theorem is needed for importing sequential verification result into the theorem proving system.

In the remainder of this section, we will briefly introduce the individual steps that we have undertaken: verifying the translator correctness theorems, proving the general importing theorems, combining the translator correctness theorems with the importing theorems on the basis of deep embedding semantics and proving the existential theorem. These will each be considered in detail in subsequent chapters.

#### 1.3.1 Verifying the MDG Translators

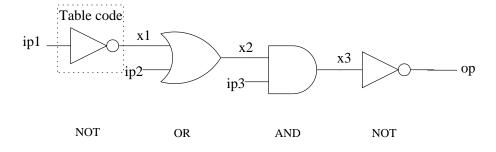

The input language of the MDG system is a Prolog-style hardware description language (MDG-HDL) [86], which allows the use of abstract variables for representing data signals. It supports structural specification, behavioral specification or a mixture of both. A structural specification is usually a netlist of components connected by signals, and a behavioral specification is given by a tabular representation of transition/output relations or a truth table. In MDG, a circuit description file declares signals and their sort assignment, components network, outputs, initial values for sequential verification and the mapping between state variables and next state variables. In the components network, there is a large set of predefined components such as logic gates, flip-flops, registers and constants, etc. Among the predefined components there is a special component called a Table, which is used to describe a functional block in the implementation and specification. The Table constructor is similar to a truth table, but allows first-order terms in rows. It also allows the high-level description to construct ITE (If-Then-Else) formulas and CASE formulas. A table is essentially a series of lists, together with a single final default value. The first list contains variables and cross-terms. The last element of the list is the output of the table which must be a variable (either concrete or abstract). For example, a two input AND gate can be described as the table as shown in Figure 1.2. In the figure, "\*" means "don't care". It states that if x1 is equal to false and x2 is DON'T CARE then the output y is equal to false, if x1 is equal to true and x2 is equal to false then the output y is equal to false, otherwise the output y is equal to true.

Most of the components in the MDG-HDL library are compiled into their own core MDG-HDL code (tabular codes) first. The core MDG-HDL program can then be compiled into an internal MDG decision graphs (MDGs). Some components, such as registers, are implemented directly in terms of MDGs. However, in theory these components also could be implemented as tables to provide general specification mechanism. We assume the MDG-HDL program is firstly translated into a core MDG-HDL program and then the core MDG-HDL program is translated into MDG.

|      | INP       | UTS  | OUTPUT |

|------|-----------|------|--------|

|      | <b>x1</b> | x2   | у      |

| IF   | F         | <br> | F      |

|      | Т         | <br> | F      |

| ELSE |           |      | Т      |

(a) AND gate table in MDG-HDL and core MDG-HDL

Figure 1.2: The AND Table MDH-HDL  $\xrightarrow{(1)}$  core MDG-HDL  $\xrightarrow{(2)}$  MDG decision graphs

Figure 1.3: Overview of the MDG Translation Phases

In this situation, the MDG system could be specified as in Figure 1.3.

Because the Table constructor allows the high-level description to construct ITE formulas and CASE formulas, the possible input value of the else condition is not listed in the table of the core MDG-HDL. For example, the possible input value for the else condition of the AND gate table should be that if x1 is equal to true and x2 is equal to true then the output y is equal to true. It is not contained in the table. However, an internal MDG decision graph is determined in terms of all possible input value of its table which could be represented as a formula representation. Therefore, the MDG system translates the core MDG-HDL program into its formula representation first. In the MDG formula representation program, the table not only contains the input value of the if condition, it also contains the possible input value of the else condition. For example, an AND gate can be described as shown in the Figure 1.4.

|      | INPUTS    |            | OUTPUT |

|------|-----------|------------|--------|

|      | <b>x1</b> | <b>x</b> 2 | y      |

| IF   | F         | <br>       | F      |

|      | Т         | F          | F      |

| ELSE | Т         | Т          | Т      |

Figure 1.4: The AND Gate in the MDG Formula Representation

$$MDH-HDL \xrightarrow{(1)}$$

core  $MDG-HDL \xrightarrow{(2)}$   $MDG$  formula representation  $\xrightarrow{(3)}$   $MDG$  decision graphs

Figure 1.5: The MDG Translation Phases

In other words, the step (2) in Figure 1.3 could be further divided into two steps. The core MDG-HDL program is translated into the MDG formula representation first and the MDG formula representation program can then be translated into an internal MDG decision graph. Now, the MDG system could be specified as in Figure 1.5.

Adopting this approach makes the translation phase more amenable to verification. We are not verifying the actual MDG implementation. Rather our formalization of the translator is a specification of it. Once combined with a translator from core MDG-HDL to MDGs, it would be specifying the output required from the implementation. This would be used as the basis for verifying such an implementation. Effectively we split the problem of verifying the translator into the two problems of verifying that the implementation meets a functional specification, and that the functional specification then meets the requirement of preserving semantics. We are concerned with the latter step here. This split between implementation correctness and specification correctness was advocated by Chirica and Martin [16] with respect to compiler correctness.

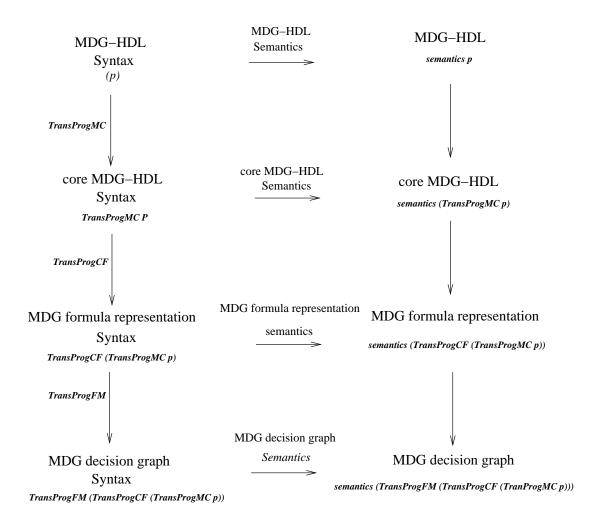

In our research, we intend to verify the translation phase of the MDG system (Figure 1.5) based on the semantics of the MDG input language using the HOL theorem prover. As we mentioned above, the MDG system can be considered as a series of translators, translating between different intermediate languages, as shown in Figure 1.6. The verification process includes the following steps. Firstly, the syntax and the semantics of the subset MDG-HDL, core MDG-HDL, MDG formula representation and MDG decision graph will be defined. A set of functions, which translate the program from MDG-HDL to core MDG-HDL, from core MDG-HDL to the MDG formula representation and from the MDG formula representation to the MDG decision graph, will then be defined. For each program in MDG-HDL, core MDG-HDL or the MDG formula representation, the compilation operators are defined as functions, which return their core MDG-HDL, the MDG formula representation or MDG decision graph code. Translation functions TransProgMC, TransProgCF or TransProgFM are applied to each MDG-HDL program, core MDG-HDL program or the MDG formula representation so that the corresponding core MDG-HDL program, MDG formula representation program or MDG decision graph program is established. In other words, the relations of the translations can be represented as below:

The standard approach to prove a translator between two languages is in terms of the semantics of the languages, shown in Figure 1.6. Essentially the translation should preserve the semantics of the source language. This has the traditional form of compiler specification correctness used in the verification of a compiler [16]. The

Figure 1.6: Compilation Correctness

analogous method can be used to specify and verify the translation part of the MDG system. For the translation to core MDG-HDL, the correctness theorem has the form

```

∀ p. Semantics (p) = Semantics (TransProgMC p)

```

For the translation to the MDG formula representation, the correctness theorem has the form

```

∀ p. Semantics (TransProgMC p) =

Semantics (TransProgCF (TransProgMC p))

```

For the translation to the MDG decision graph, the correctness theorem has the form

```

∀ p. Semantics (TransProgCF (TransProgMC p)) =

Semantics (TransProgFM (TransProgCF (TransProgMC p)))

```

By combining the three correctness theorems above, we can obtain a correctness theorem. This theorem states that the semantics of the low level MDGs is equal to the semantics of the high level MDG-HDL.

The MDG system is based on Multiway Decision Graphs which extend ROBDDs with concrete sorts, abstract sorts and uninterpreted function symbols. It can also deal with the boolean subset as other ROBDD tools do. For the sake of easily applying our method to the other decision graph based verification tools, we will define the deep embedding semantics for two different subsets of the MDG-HDL language in this thesis. Both subsets we considered in this thesis do not contain

three MDG predefined components (Multiplexer, Driver and Constant) and the Transform construct used to apply functions. These components are omitted from our subsets as they have non-boolean inputs or outputs. We make the subset simple here since we want to explore the feasibility of this method.

The first subset is a boolean subset of the language which corresponds to a ROBDD system. In this subset, the table representation in the core MDG-HDL language only can be defined in terms of the corresponding boolean inputs value (true or false). We consider this subset because it corresponds to a ROBDD system. The formalization of this subset can be integrated to other ROBDD based tools with relatively small modification. For this subset, we will concentrate on verifying the first two translation steps (see (1)(2), Figure 1.5). Detail will be discussed in Chapter 3.

The second subset is an extension of the first subset. In the rest of this thesis we will call it the extended subset. This subset allows the program of the MDG-HDL language to contain concrete sorts. In other words, the subset we considered in this thesis is a subset language of MDG-HDL whose inputs and outputs of a table could be boolean sorts and concrete sorts. This is very important because this is the way the MDG system works. For coping with different types in one list, we define a new type Mdg\_Basic in HOL. The value of the type can be either a boolean value or a string. As a result, the syntax and the semantics of this subset are more complex and the difficulty of the MDG translator verification will be increased a lot. For this subset, we will concentrate on verifying the first translation step (see (1), Figure 1.5). More detail will be discussed in Chapter 4.

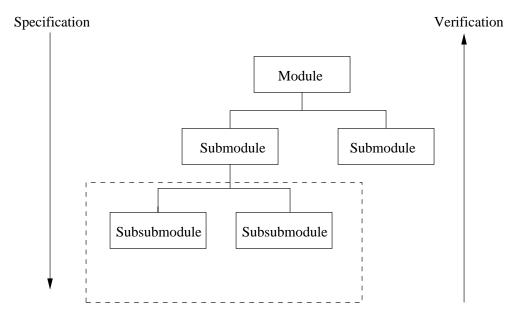

#### 1.3.2 The Importing Theorems

Generally, when we use HOL to verify a design, the design is modelled as a hierarchy structure with modules divided into submodules as shown in Figure 1.7. The submodules are repeatedly subdivided until the logic gate level is eventually

Figure 1.7: Hierarchical Verification

reached. Both the structural and the behavioral specifications of each module are given as relations in higher-order logic. The verification of each module is carried out by proving a theorem asserting that the implementation (its structure) implements (implies) the specification (its behavior). They have the very general form:

$$implementation \supset specification$$

(1.1)

The correctness theorem for each module states that its implementation down to the logic gate level satisfies the specification. The correctness theorem for each module can be established using the correctness theorems of its submodules. In this sense the submodule is treated as a black-box. A consequence of this is that different technologies can be used to address the correctness theorem for the submodules. In particular, we can use the MDG system instead of HOL to prove the correctness of submodules.

In order to convert the MDG verification results into HOL, we need to formalize the results of the MDG verification applications in HOL. These formalizations have different forms for the different verification applications, i.e., combinational verification gives a theorem of one form, sequential verification gives a different form and so on. However, the most natural and obvious way to formalize the MDG result does not give theorems of the form that HOL needs if we are to use traditional HOL hardware verification techniques. Therefore, we need to be able to convert the MDG results into a form that can be used. In other words, we need to prove a series of translation theorems (one for combinational verification and one for sequential verification, etc.) that state how an MDG result can be converted into the traditional HOL form:

```

Formalized MDG result ⊃

(implementation ⊃ specification)

```

We have formally specified the correctness results produced by several different MDG verification applications. We have given a general importing theorem for some MDG applications. These theorems do not explicitly deal with the MDG-HDL semantics or multiway decision graphs. Rather they are given in terms of general relations on inputs and outputs. The theorems proved could be applicable for other verification systems with similar architectures based on reachability analysis or equivalence checking.

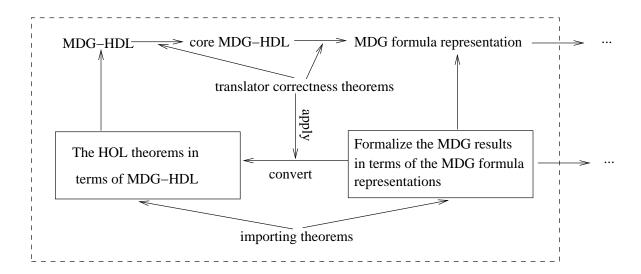

## 1.3.3 Combining the Translator Correctness Theorems with the Importing Theorems

In this section, we will introduce the basic idea about how to combine the translator correctness theorems with the importing theorems based on the deep embedding semantics. This combination allows the MDG results to be reasoned about in HOL in terms of the MDG input language (MDG-HDL). Ultimately in HOL we want a theorem about input language artifacts. However, the MDG verification results are obtained based on a low level data structure – a MDG representation: that is what the algorithms apply to. Therefore, the formalization of the MDG verification results in the importing theorems ought to be based on the semantics of the MDG

representations. However, the theorem about the translator's correctness can be used to convert the result MDG proves about the low level representation to one about the input language (MDG-HDL). By combining the translator correctness theorems with the importation theorems, we obtain the new importing theorems which convert the low level MDG verification results into HOL to form the HOL theorems in terms of the semantics of a high level language – MDG-HDL. In other words, we are not only able to import the MDG results into HOL based on a verified MDG system, but also the MDG verification results can be converted to the theorems of HOL in terms of the semantics of MDG-HDL.

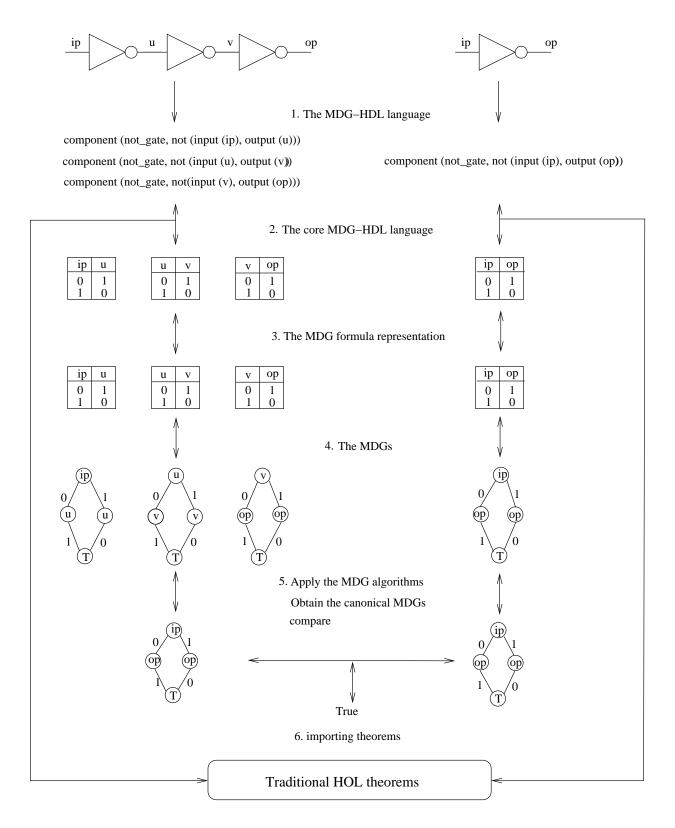

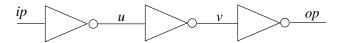

For example, if we check that three NOT gates are equivalent to a single NOT gate, the whole MDG verification process and the importing process can be illustrated in Figure 1.8. In the Figure 1.8, step (1) gives a main part of the two circuit description files (the MDG-HDL input language), which are translated into the core MDG-HDL (tabular representations) language as shown in step (2). The core MDG-HDL languages are then translated into the MDG formula representation language (step (3)). The MDG formula representation languages are further translated into the MDG decision graph language (step (4)). A set of the MDG algorithms is then applied to the MDGs in order to obtain two canonical MDGs and the MDG tool checks whether two canonical MDGs are identical and returns true or false (step (5)).

In our example the MDG tool returns true. The MDG verification results are obtained based on the low level MDGs rather than the high level language MDG-HDL. However, the translator correctness theorems state that the semantics of the low level MDG is equal to the semantics of the high level MDG-HDL (the MDG input language). By combining the translator correctness theorems, the MDG verification results can be imported into HOL based on the semantics of the MDG input language (MDG-HDL). Therefore, the traditional HOL theorem can be obtained in terms of the semantics of the MDG input language.

In this thesis, we will prove two translators for the boolean subset and one

Figure 1.8: The MDG Verification Process

translator for the extended subset. In order to demonstrate the combination of the translator correctness theorems and the importing theorems, the formalization of the MDG results will be in terms of the MDG formula representation for the boolean subset and the core MDG-HDL for the extended subset. In fact, the principle is the same. Similar conversion can be done for further translators if we prove corresponding translators. By combining the translator correctness theorems with the importation theorems, we obtain the new importing theorems which convert the low level MDG verification results into HOL to form the HOL theorems in terms of the semantics of MDG-HDL. The combination also allow the additional assumption for sequential verification to be proved in terms of the semantics of MDG-HDL and the conversion theorem to be obtained in terms of the semantics of MDG-HDL.

#### 1.3.4 Proving the Existential Theorem

In the traditional HOL hardware verification, when we prove a design, we need to prove a theorem stating that the implementation of the design implements its specification.

$$\forall$$

ip op. IMPL ip op  $\supset$  SPEC ip op

However, this representation might meet an inconsistent model that trivially satisfies any specification. This is sometimes called the "false implies anything problem" [14]. If the implementation (IMP ip op) of a design is false for all the inputs and outputs, then this implication is a theorem, no matter what constraint is imposed on the variables by its SPEC ip op. This is wrong because a theorem like this provides no meaning to ensure the correctness of the circuit. One solution to this problem is to verify a stronger consistency theorem against the implementation as suggested in [58], which has the form:

$$\forall$$

ip.  $\exists$  op. IMPL ip op

This means that for any input ip there is an output op which is consistent with it.

On the other hand, when we formally import the MDG verification results into HOL to form the HOL theorems [80], we should prove an additional assumption against the specification. This theorem states that for all possible input traces, the behavior specification SPEC ip op can be satisfied for some outputs:

$$\forall$$

ip.  $\exists$  op. SPEC ip op

This means that the machine must be able to respond to whatever inputs are given.

For ease of importing of MDG results into HOL for sequential verification and also for avoiding an inconsistent model, we will summarize a general way to prove theorem which has the form below:

$$\forall$$

ip.  $\exists$  op.  $C$  ip op

where C represents any circuit, and ip, op represent external input and external output respectively. We called it the existential theorem [83]. More detail will be discussed in Chapter 7.

#### 1.4 Outline of Thesis

The thesis is organized as follows:

In Chapter 2, we give a review of the literature most directly related to our research. We discuss embedding a hardware description language (HDL) in a proof system, previous work on verifying verification systems, an overview of compiler verification work and technologies used in the combination of different verification systems.

In Chapter 3, we investigate the verification of the translation phases of a simplified version of the MDG system (boolean subset) based on a theorem prover system (the HOL system). This can be viewed as a simple compiler correctness problem. We define a deep embedding formal semantics of the MDG-HDL language, the core MDG-HDL language and the MDG formula representation in higher order logic. A set of functions for translating the MDG-HDL subset language to their core MDG-HDL language and translating the core MDG-HDL language to their MDG formula representation language are given. The correctness theorems of the translation which quantifies over syntactic structure are verified. In particular, we demonstrate that this compiler specification preserves the correctness results produced by the MDG verification system.

In Chapter 4, we investigate the verification of the translation phases for the extended subset. We extend our formalization to accommodate a list of inputs (the first argument of the table component) with boolean sorts and concrete sorts. For this subset, we prove the first translator. We define the formal syntax and semantics of the MDG-HDL language and core MDG-HDL language. A set of functions for translating this subset language to their core MDG-HDL equivalent has then been given. The correctness theorem about the translation, which quantifies over its syntactic structure, has been proved.

In Chapter 5, we describe how to convert the MDG results into theorems for use in the HOL system. The MDG system combines a variety of different hardware verification applications including combinational verification, sequential verification, invariant checking and model checking. We give a general importing theorem for converting MDG results of the different applications (except model checking) into HOL. The theorems proved do not explicitly deal with the MDG-HDL semantics or multiway decision graphs. They are given in terms of general relations on inputs and outputs. Thus they are applicable to other verification systems with a similar architecture.

In Chapter 6, we show how to combine the translator correctness theorems with

the importing theorems for two subsets. This combination allows the MDG results to be reasoned about in HOL in terms of the MDG input language (MDG-HDL). The two different MDG verification applications have been formalized in terms of the semantics of the low level language and imported into HOL to form the HOL theorems in terms of the semantics of MDG-HDL. In other word, the low level MDG verification result has been converted into a high level form which is usable in a traditional HOL hardware verification.

In Chapter 7, we summarize a general way of proving the existential theorem for the implementation and specification of any design based on the syntax and the semantics of MDG-HDL. This theorem is needed when importing the MDG sequential verification result into HOL and avoiding an inconsistent model be produced.

In Chapter 8, we use a simple example, the verification of the correctness theorem and usability theorems for a vending machine, to demonstrate the feasibility of our approach. We have verified the correctness of the vending machine in MDG. This has been imported into HOL to form the HOL theorem. We have then proved a usability theorem about a specification of the vending machine in HOL. By combining the imported theorem and specification based usability theorem, we obtain a usability theorem about the vending machine implementation.

In Chapter 9, we conclude the thesis and indicate the future work.

### **Summary**

This chapter has motivated our emphasis on dependability of the hybrid system, and situated our approach which aims to import the MDG results into HOL in a trusted way. It also has indicated that we are concerned with how great a degree of trust the MDG system has, how to formally justify the conversion of the MDG results into the traditional HOL hardware verification theorems and how to formally link two

systems in a natural way. This chapter has pointed out that the deep embedding semantics play a very important role in our research. On the one hand, the deep embedding semantics could be used to verify the correctness of aspects of the MDG system using the HOL system. On the other hand, based on the verified MDG system, the deep embedding semantics is used to combine the translator correctness theorems with the importing theorems, allowing the MDG results to be reasoned about in HOL naturally.

## Chapter 2

## Literature Review

Combining theorem proving systems with symbolic state enumeration systems opens a way for theorem proving systems to be applied more widely to the real world. Many researchers are working in these areas to contribute their ideas and approaches. In this thesis, we will focus on the verification of a symbolic state enumeration system (the MDG system) and provide a theoretical underpinning to the formal linkage of a symbolic state enumeration system and a theorem proving system (MDG and HOL). We first verify the correctness of translators of the MDG system by using the HOL system. This can be viewed as a simple compiler correctness problem. We next prove theorems that formally convert the MDG verification results of the MDG different applications into the traditional HOL hardware verification theorems in the style of Gordon [35]. By combining the translator correctness theorems with the importing theorems, the MDG verification results can be imported into HOL in terms of MDG-HDL. Our work is concerned with embedding a hardware description language (HDL) in a proof system, verifying verification systems, compiler verification and trusting combined systems. This chapter gives a literature review which is related to our research and divided into the corresponding subsections listed below:

• We briefly introduce embedding an HDL in a proof system.

- We discuss previous work on verifying verification systems.

- An overview of compiler verification work is given.

- We review the different technologies that have been used to combine the theorem proving systems with other systems and talk about the combined approaches and the degree of trust of the system. We then propose our own ideas.

## 2.1 Semantic Embedding

Semantic embedding is an approach to defining precise semantics of HDLs inside the logic so as to support the use of HDLs within a general theorem proving environment. Many researchers are aiming to find a tractable semantics for the hardware description languages such as VHDL [64]. For example, Reetz and Kropf [55] defined the semantics of a significant subset of VHDL in HOL to formalize a compiler generator. Gordon [31] defined three different semantics (event semantics, trace semantics and cycle semantic) for a subset of VHDL for use in the different applications.

There are two ways to represent the semantics of HDLs inside logic: deep embedding and shallow embedding. With a deep embedding, a type syn, is defined inside the logic to represent HDL texts. A type, sem, that represents the semantics is also defined, and then a semantic function, meaning: $syn \rightarrow sem$ , is defined, by structural induction over syn [33] [32] [7]. With a shallow embedding there is no type syn or semantics function inside the logic. Instead a parser is used to translate HDL texts directly into terms of the logic. Each of these has advantages and disadvantages. The advantage of deep embedding is that it allows reasoning about classes of programs and so about the general properties of the programs. However, setting up types of abstract syntax and semantics is much work. The advantage of shallow embedding is that this work is avoided, because the process of assigning meaning to the texts does not have to be encoded as a function inside the logic.

A meta-language program can easily compute differently typed terms for different HDL texts.

Brock and Hunt [10] described a simple hardware description language in the Boyer-Moore theorem prover. It lacks delays and does not permit recursion: it thus deals with combinational logic only. However, this is the earliest research known to us which defines a deep embedding operational semantics for an HDL in a proof system. In their work, circuits were represented as list constants, which were interpreted by a semantics function. This semantics function traversed valid abstract syntax categories. The circuit descriptions were hierarchically composed. A well-formed predicate was defined to check that these definitions are purely combinational.

Melham [58] deeply embedded a denotational semantics of a CMOS circuit inside the HOL system, which is an ideal example for getting the general idea about deep embedding. He defined an abstract data type representation of CMOS circuit descriptions. A semantics function was given in terms of the environments which mapped circuits to a formula describing their switch-level behavior. The environment with the type  $:string \rightarrow bool$  mapped strings string, denoting wire names, to their values.

Boulton et al [7] embedded semantics of three different hardware description languages in higher-order logic (HOL-ELLA, HOL-SILAGE, HOL-VHDL). Both the HOL-ELLA and the HOL-SILAGE projects used shallow embedding. The HOL-VHDL project used deep embedding. In their paper, they compared the two approaches used in three different projects and summarized the benefits of the general technique of embedding a conventional notation in a mechanized formal system and indicated that embedding the HDL semantics allows the practical tool to act directly on logic representations and thereby the designs can be reasoned about in a proof system.

Goossens [30] investigated the integration of HDLs and automated proof systems.

His aim was to clarify the semantics of the particular HDL and to present a more standard interface to formal methodologies. A formal static and dynamic operational semantics for a subset of the industrial HDL ELLA [28] were embedded within the LAMBDA proof system.

In this thesis, we deeply embed two subsets of MDG-HDL into HOL. We obtain the logic representation of each MDG-HDL program, which could be reasoned about directly into HOL. However, our aim is to verify the correctness of aspects of the MDG system by using the HOL system and to provide a formal linkage between the MDG system and the HOL system in terms of the deep embedding semantics. We use the embedding semantics to prove the translation phases of the MDG system. Our semantics explicitly represent the relation with the external wires. This representation can be used in formalizing the MDG verification results and importing the MDG results into HOL naturally. We utilize this fact to allow MDG to be used when it would be easier than obtaining the result directly in HOL.

## 2.2 Verifying Verification Systems

Different technologies have been used to ensure the correctness of verification systems. In a sense, which method is chosen depends on the architecture of the verification system. The Edinburgh LCF [34] (Logic of Computable Functions) family of theorem provers (including HOL) uses an abstract data type (Thm) to represent theorems. The type checker ensures the theorems can only be constructed by applying a small number of primitive inference rules. There is no method to construct a theorem except by carrying out a proof based on the primitive inference rules and axioms. This increases the reliability of the system. For HOL, these primitive inference rules have been proved sound via a set-theoretic semantics [40]. Pottinger [68] has also proved that they are complete with respect to Henkin's general models (the methods that Henkin used to establish completeness for systems of second-order and higher-order logic). In this way if we guarantee the primitive inference rules correct

then invalid theorems can be avoided.

The LCF approach also permits proofs to be recorded. Proofs can be stored in files and be represented by lists of inferences. It allows us to make use of the availability of the sequence of inferences and to check the consistency of each inference automatically. Wong [77], changed the HOL system so as to be able to record each proof and store it into proof files. He developed a proof checker to examine the correctness of the proof files - lists of inferences generated by the HOL system. The proof checker first took a proof file as an argument and then checked whether the proofs were correct or not. A log file was then produced that contained the hypotheses, lemmas used by the proof and the resulting theorem of the proof. The application of this method is significant in developing safety-critical and highintegrity systems where high confidence of correctness is required. Since a proof checker accepts the proof files containing only primitive inference rules, it may possibly be verified formally. The proof checker also provided an independent means of ensuring the validity and consistency of the proof. Some other theorem provers such as Ngthm [9] and Coq [48] already store proof trees in the system. Boyer and Dowek [8] specified and implemented a proof checker in Nqthm logic.

Is the proof checker itself correct? If the proof checker can be formally verified, it will greatly increase the confidence in the consistency of checked proofs. Since the proof checker is relatively simple, it is easier to verify than a full system. Von Wright [75] formalized the specification of a proof checker in HOL. In his work, he carefully analysed what constituted a HOL proof, formalized the syntax of the terms, types, and theorems, and defined predicates to represent the primitive inference rules. He also demonstrated how the HOL system had been used to formally verify the specification of a proof checker for higher-order logic proofs [76]. An alternative method of using refinement to verify the proof checker was also suggested by von Wright [74].

The architecture of the symbolic state enumeration based verification systems is different. In some of these systems, higher level languages such as hardware

description languages are used to describe the specifications and implementations. The specifications and implementations are then translated into decision graphs. A series of algorithms in the system is used to efficiently and automatically deal with the decision graphs and obtain the correctness results. For verifying such systems, we need to prove the translators from the higher level languages into decision graphs, and to prove the algorithms correct that are used to manipulate the decision graphs.

Homeier and Martin [46] used the HOL system to verify a verification system called a verification condition generator (VCG) for a simple programming language. Since the VCG translated the annotated programs to the lists of verification conditions, the proof of the correctness of the VCG could be considered as an example of a compiler correctness problem. In other words, the proof of the correctness of the VCG can be obtained by proving a translator. The semantics of the annotated programs and verification conditions were formalized in HOL. The correctness theorems showed that the truth of the verification conditions implied the truth of the annotated programs.

Chou and Peled [17] used the HOL system to verify a non-trivial algorithm - the Partial-Order reduction technique, implemented in the protocol tool SPIN. This algorithm is used to cut down the state-space exploration performed by model checkers. They built up the groundwork of a formal infrastructure that included the mathematical support for proving various automatic verification algorithms. Their results not only gave more confidence in the algorithm but also demonstrated formal verification is a practical and useful tool.

In this thesis, we investigate the correctness of aspects of the MDG system (figure (2.1)) by using HOL. Verifying the algorithms is beyond the scope of this thesis which can be done similarly to Chou and Peled's work. We consider verifying the translation process is correct based on the deep embedding semantics. We need to verify the translator preserves the semantics of a program through the translation between languages as suggested for Homeier's work [78] [81] [79]. A difference is that Homeier used a compiler verification method to verify a software verification system.

Figure 2.1: The MDG Verification System

We used a similar method to verify a hardware verification system. We consider verifying the correctness of aspects of the MDG system. In the next section, we will review previous work that has been done on the compiler correctness problem.

## 2.3 Verifying Compiler Correctness

The literature on compiler correctness is large. The earliest example was described more than thirty years ago [56]; this reported how McCarthy and Painter successfully verified the correctness of a simple algorithm for compiling arithmetic expressions into machine language on an ideal machine. The syntax and semantics of the source and object language were given. The compiler correctness theorem stated that the semantics of the source program preserved the semantics of the target code. Their basic idea is still being used in compiler verification.

At the same time, Burstall and Landin [13] first proposed the use of algebraic

methods to verify compiler correctness. The key contribution from the algebraic approach to compiler correctness was to reject the simple function to be used as a compiler and impose structure on the program involved. Many researchers have developed this method including Morris [62] [63] and Chirica [15]. A tutorial introduction to the algebraic method was given by Collier [19]. However, the early work focused on the basic methodology rather than verifying a real language. People could not deal with the tedium of formal proof if they verified a compiler by hand.

With the development of mechanical assistance systems, researchers began to verify some simple imperative languages by using mechanical checking technology. Milner and Weyhrauch [59] used the Stanford LCF system to mechanically check the formal verification of a compiler for a simple imperative language. Cohn and Milner [18] used the Edinburgh LCF system to prove a simple parsing algorithm. In their paper, a generally mechanized method of deriving structural induction rules within the system was discussed. Chirica and Martin [16] considered the problem of proving the correctness of parsing and syntax analysis. They indicated that a compiler implementation should specify exactly how the compiler was implemented to generate the object code. The correctness of a compiler implementation is verified by comparing corresponding object programs generated by the compiler specification and implementation. However, most work including those mentioned above considered a very simple language and the target machine was idealized (no finite limitations on word size and memory size).

In 1989, Young [85] verified a code generator which was one level of a stack of verified system components by using a Boyer-Moore theorem prover (the Boyer-Moore prover is a theorem prover for a quantifier-free first-order classical logic with equality). Their source language was a subset of Gypsy [29] and the target language was the Piton [61] assembly level language. The operational semantics for a subset of Gypsy and Piton was given. Functions were implemented in the Boyer-Moore logic that translated Gypsy programs into Piton. The correctness of the translator was mechanically checked. Moore [60] verified that Piton was successfully implemented

on a general purpose microprocessor (FM8502) by using the Boyer-Moore theorem prover.

Other notable work is that of Joyce [50], who described the formal specification and verification of a compiler for a very simple imperative programming language on an non-idealized target machine. The semantics for this programming language, the target machine and the compiler were all specified in higher-order logic. Inference rules of higher-order logic were used to construct a formal proof showing that compiled programs execute according to the semantics of the language. A compilation process was split into two phases for controlling the complexity of the formal proof of correctness. The first phase compiled the hierarchically structured program into a flat intermediate form. The second phase compiled the intermediate form into target machine code.

At the same time, Gordon [37] did the original work of constructing within HOL a framework for proving the correctness of a program. He used a shallow embedding [7] (i.e. only the semantics is represented in the HOL logic) to embed the program logic in the HOL logic. HOL is a foundational system which means that one can define new constants in a way that does not affect the logical consistency of the system. In other words, thus means the embedding of a language can be obtained by using constant definitions rather than by introducing arbitrary axioms to describe the semantics.

Curzon [22] successfully used the HOL system to verify compilers for a subset of the structured assembly language Vista, for a real microprocessor, VIPER. The compiler correctness work was based on a general model of I/O. The verification of a generic compiler from a generic version of Vista to a generic flat assembly code had been considered. This made it possible to verify a compiler from different versions of Vista to the VIPER microprocessor or to other similar machines easily (i.e. you just need to change some basic configurations). He also combined the verified compiler with a derived programming logic so that the corresponding properties of the compiled code can be automatically derived.

Our work concernes with verifying the correctness of the translators that translates a subset of the MDG input language MDG-HDL into the low level languages. Curzon et al. [26] did some basic work which verified the MDG components library in HOL. In their paper, the semantics of the TABLE had been first formalized in HOL. The semantics of the MDG-HDL components was in the style of Gordon. They had verified the table implementations of each of the hardware components that were implemented in terms of tables in the MDG system.

The work presented in this thesis is based on previous work to verify the MDG components library in HOL [26] and builds on the work of Curzon [22] concerned with compiler verification. The source and target languages are different to his. Our source language is a netlist level hardware description language and our target language is the core MDG-HDL language and the MDG formula representation language. We only consider the correctness of a compiler specification in this thesis. We define a deep embedding formal semantics for a subset of MDG-HDL and the corresponding low level languages in higher-order logic. However, the structures of the proofs are similar and also have been mechanically checked by using the HOL system. Most importantly, we are trying to investigate and develop a method that links compiler correctness to the combination of two different verification systems (MDG and HOL), rather than just verifies the correctness of a compiler specification.

### 2.4 Trusting Combined Systems

Recently, researchers have paid much attention to combining theorem provers and other symbolic computation systems. Theorem provers have been linked to other theorem provers [49], to model checkers [51] [2] [39] and to computer algebra systems [42]. Methodologies for co-operation between systems are dependent on properties of the system. The motivation for combining different systems is to achieve the benefits of them both and to make the verification simpler and more effective.

A common approach to combining proof tools is to use an automated tool as an oracle to provide results to the interactive proof process. Joyce and Seger [51] presented a hybrid verification system: HOL-Voss. In their system, several predicates were defined in the HOL system, which presented a mathematical link between the specification language of the Voss system (symbolic trajectory evaluation) [44] and that of the HOL system. As a result this link caused the specification language of Voss to become a subset of the language of the HOL system. In other words, trajectory evaluation was used as a decision procedure for the HOL proof system. A HOL tactic, VOSS\_TAC, which was implemented as a remote function, was written. This tactic enabled some HOL goals to be proved by calling symbolic trajectory evaluation and mirroring the results (true or false) in HOL. If it is true, then the assertion will be transformed into a HOL theorem and this theorem can be used by the HOL system to derive additional verification results. Zhu et al. [87] successfully applied HOL-Voss to the verification of the Tamarack-3 microprocessor.