Hardware Verification Group Home > Research > Methodologies and Frameworks >

Model Order Reduction using SPICE Simulation Traces

Paul Winkler ,

Henda Aridhi,

Mohammed Zaki Hussein and

Sofiene Tahar

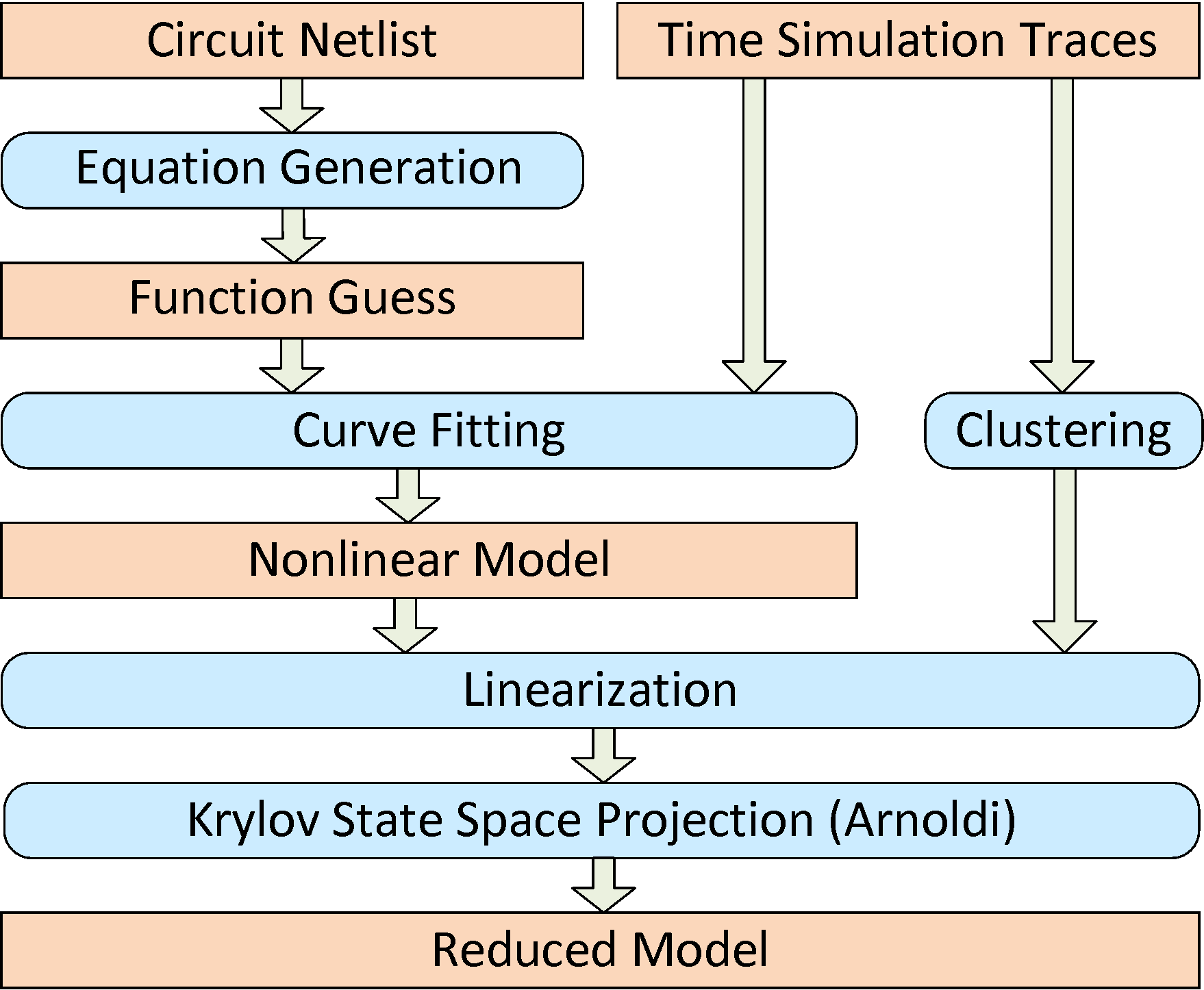

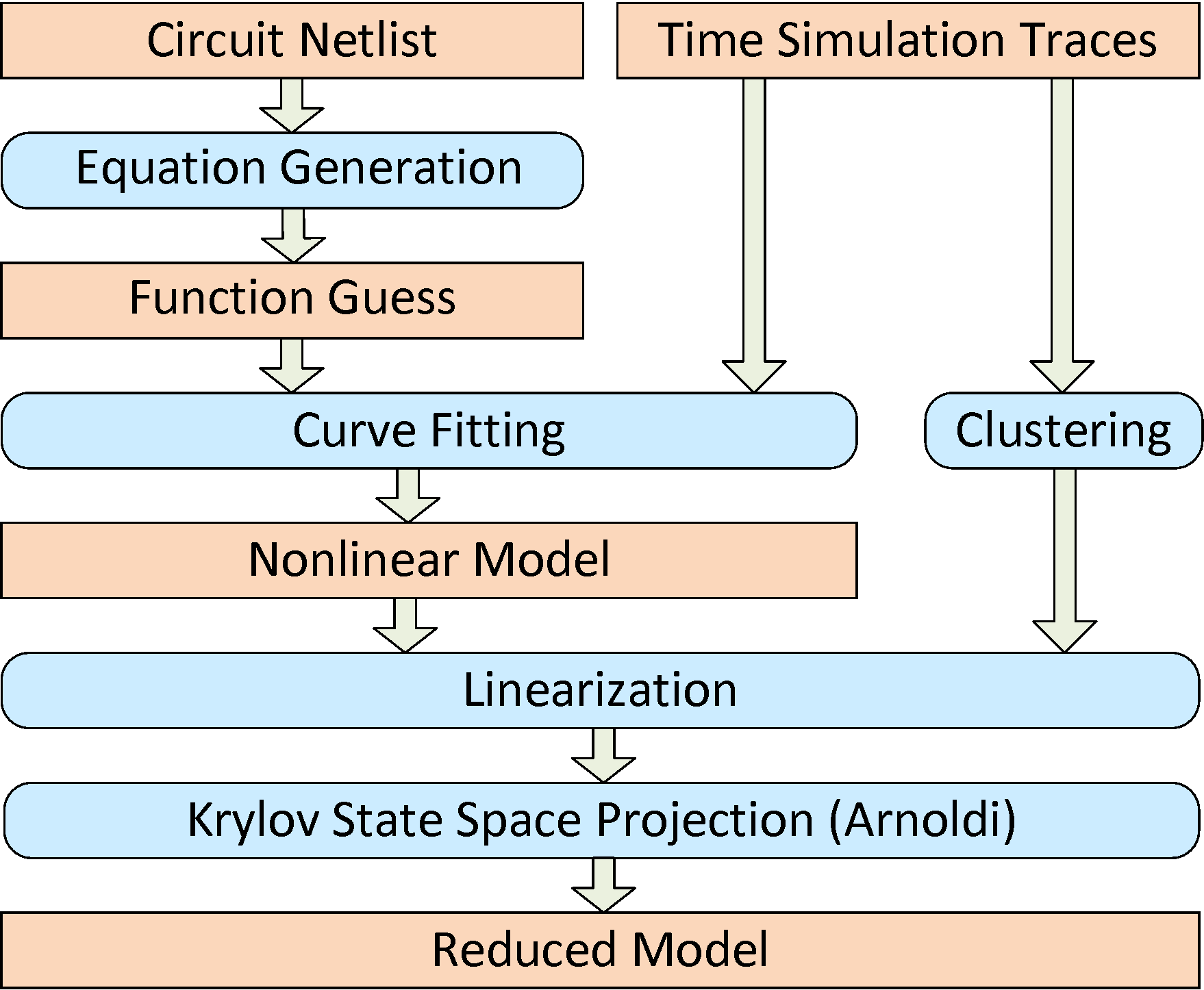

The generation of fast models for device level circuit descriptions

is a very active area of research. Model order

reduction is an attractive technique for reducing the computational cost of dynamical models

simulation. In this work, we propose an approach based

on clustering, curve-fitting, linearization and Krylov space

projection to build reduced models for nonlinear analog circuits.

We demonstrate our model order reduction method

for three nonlinear circuits: a voltage controlled oscillator,

an operational amplifier and a digital frequency divider. Our

experimental results show that the reduced models lead to

an improvement in simulation speed while providing the same behavior of the original circuit design.

Files

Files