# UNIVERSITÉ DE MONTRÉAL

# MULTILEVEL MODELING, FORMAL ANALYSIS, AND CHARACTERIZATION OF SINGLE EVENT TRANSIENTS PROPAGATION IN DIGITAL SYSTEMS

GHAITH BANY HAMAD

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

THÈSE PRÉSENTÉE EN VUE DE L'OBTENTION DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (GÉNIE ÉLECTRIQUE) AVRIL 2017

# UNIVERSITÉ DE MONTRÉAL

# ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# MULTILEVEL MODELING, FORMAL ANALYSIS, AND CHARACTERIZATION OF SINGLE EVENT TRANSIENTS PROPAGATION IN DIGITAL SYSTEMS

présentée par : BANY HAMAD Ghaith

en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment acceptée par le jury d'examen constitué de :

- M. AUDET Yves, Ph. D., président

- M. SAVARIA Yvon, Ph. D., membre et directeur de recherche

- M. AIT MOHAMED Otmane, Ph. D., membre et codirecteur de recherche

- M. BELTRAME Giovanni, Ph. D., membre

- M. LEVEUGLE Regis, Ph. D., membre externe

# **DEDICATION**

To my beloved parents, Ibtissem, Lynne, my brothers, and my sisters.

#### ACKNOWLEDGEMENTS

It has been an amazing experience to accomplish my Ph.D. thesis at Polytechnique Montreal and Hardware Verification Group (HVG). It certainly would not have happened without the support and guidance of several people to whom I owe a great deal.

First of all, I would like to thank my supervisor, Dr. Yvon Savaria. He was fully supportive, understanding, involved and present during all the phases of my research. I have learned many things from him in regard to research, academia, and life in general.

Secondly, I sincerely thank Prof. Otmane Ait Mohamed, for co-supervising my research work. This thesis would not have been possible without his guidance, his expert advice, his support and encouragements. He introduced me to the topic of this thesis and guided me in the right direction. Next, let me thank all the members of HVG for their help and encouragement. Their friendship brought me a warm environment in the lab. Especially, I thank Ibtissem Seghaier and Marwan Ammar.

Last but not least, I thank my family for their constant moral support and their prayers. They are the people who are closest to me and suffered most for my higher study in abroad. Their support was invaluable in completing this thesis.

# RÉSUMÉ

La croissance exponentielle du nombre de transistors par puce a apporté des progrès considérables aux performances et fonctionnalités des dispositifs semi-conducteurs avec une miniaturisation des dimensions physiques ainsi qu'une augmentation de vitesse. De nos jours, les appareils électroniques utilisés dans un large éventail d'applications telles que les systèmes de divertissement personnels, l'industrie automobile, les systèmes électroniques médicaux, et le secteur financier ont changé notre façon de vivre. Cependant, des études récentes ont démontré que le rétrécissement permanent de la taille des transistors qui s'approchent des dimensions nanométriques fait surgir des défis majeurs. La réduction de la fiabilité au sens large (c.-à-d., la capacité à fournir la fonction attendue) est l'un d'entre eux. Lorsqu'un système est conçu avec une technologie avancée, on s'attend à ce qu' il connaît plus de défaillances dans sa durée de vie. De telles défaillances peuvent avoir des conséquences graves allant des pertes financières aux pertes humaines.

Les erreurs douces induites par la radiation, qui sont apparues d'abord comme une source de panne plutôt exotique causant des anomalies dans les satellites, sont devenues l'un des problèmes les plus difficiles qui influencent la fiabilité des systèmes microélectroniques modernes, y compris les dispositifs terrestres. Dans le secteur médical par exemple, les erreurs douces ont été responsables de l'échec et du rappel de plusieurs stimulateurs cardiaques implantables.

En fonction du transistor affecté lors de la fabrication, le passage d'une particule peut induire des perturbations isolées qui se manifestent comme un basculement du contenu d'une cellule de mémoire (c.-à-d., Single Event Upsets (SEU)) ou un changement temporaire de la sortie (sous forme de bruit) dans la logique combinatoire (c.-à-d., Single Event Transients (SETs)). Les SEU ont été largement étudiés au cours des trois dernières décennies, car ils étaient considérés comme la cause principale des erreurs douces. Néanmoins, des études expérimentales ont montré qu'avec plus de miniaturisation technologique, la contribution des SET au taux d'erreurs douces est remarquable et qu'elle peut même dépasser celui des SEU dans les systèmes à haute fréquence [1], [2]. Afin de minimiser l'impact des erreurs douces, l'effet des SET doit être modélisé, prédit et atténué. Toutefois, malgré les progrès considérables accomplis dans la vérification fonctionnelle des circuits numériques, il y a eu très peu de progrès en matiàre de vérification non-fonctionnelle (par exemple, l'analyse des erreurs douces). Ceci est dû au fait que la modélisation et l'analyse des propriétés non-fonctionnelles des SET pose un grand défi. Cela est lié à la nature aléatoire des défauts et à la difficulté de modéliser la variation de leurs caractéristiques lorsqu'ils se propagent. En outre, plusieurs

détails manquent à haut niveau d'abstraction concernant la structure des circuits et les caractéristiques des SET. Ainsi, plusieurs hypothèses sont généralement envisagées pour modéliser le comportement des SET dans des analyses de haut niveau, ce qui affecte l'exactitude des résultats obtenus. Par conséquent, une détection à faible coût des erreurs douces dues aux SET est très difficile et exige des techniques de vérification plus sophistiquées.

Le présent travail présente une méthodologie multi-niveau (niveau transistor, porte logique, et transfert de registres) permettant de modéliser, d'analyser et d'estimer le taux d'erreurs douces induites par des événements singuliers (SEU). La méthodologie proposée étudie la dépendance des caractéristiques des SET aux formes d'ondes en entrée, aux chemins de propagation, à la polarité des impulsions, aux chemins divergents et à la re-convergence dans le circuit au niveau transistor. De nouveaux résultats sur la propagation des SET à travers différentes combinaisons de logique statiques et de logique TSPC sont présentés. Le comportement observé est ensuite caractérisé pour refléter avec précision la propagation des SET à des niveaux d'abstraction plus élevés.

Au niveau portes logiques, plusieurs techniques de vérification de la propagation des SET sont développées en se basant sur des méthodes formelles et des détails appris à bas niveau, aux niveaux transitors et masques. Dans ce travail, la modélisation formelle et l'analyse de la propagation des SET repose sur les Graphes de Décision Multivoie (MDGs) et les Théories de la Satisfiabilité Modulo (SMT). De nouvelles méthodes qui consiédèrent en même temps l'impact des effets de masquage, de la variation de largeur et des chemins re-convergents ont été développées. Les résultats ainsi obtenus montrent que la méthode de modélisation et d'analyse SMT proposée améliore de façon significative l'efficacité des analyses SET en termes de: 1) précision dans la mesure où elle donne des estimations exactes de la sensibilité aux SET appris à partir des modèles de portes logiques extraits des masques. Ces résultats ont permis d'acquérir de nouvelles connaissances sur la vulnérabilité des circuits combinatoires aux SET; 2) rapidité étant donné qu'elle est plus rapide que les techniques contemporaines; 3) extensibilité comme elle peut manipuler des circuits larges et complexes tels qu' un multiplicateur 128 bits. De plus, en se basant sur les résultats de ces analyses au niveau portes logiques, des tables de propagation sont développées pour résumer les comportements de propagation des SET.

Au niveau transfert de registre (RTL), cette thèse présente une méthodologie hiérarchique et multi-niveaux pour estimer le taux des erreurs douces dans les circuits combinatoires. La méthodologie repose sur la méthode de vérification des modèles et les tables de propagation au niveau porte logique. La conception RTL est décomposée en sous-composantes et chaque composante est à son tour annotée avec des détails provenant du niveau transistor.

De nouvelles méthodes d'abstraction et de réduction de la conception sont ensuite proposées en fonction des tables de propagation et de la structure du circuit. En outre, deux modèles différents ont été proposés reposant sur le modèle MDG et le processus de décision markovien (MDP) qui sont ensuite analysés à l'aide des vérificateurs de modèles MDG et PRISM, respectivement. De plus, une nouvelle méthode pour estimer le taux d'erreur douces (SER) est proposée. Afin d'illustrer l'utilité pratique de ces techniques de modélisation et d'analyse, nous avons analysé différents circuits combinatoires. Les approches de modélisation et d'abstraction proposées abaissent considérablement le temps et la mémoire liés à la modélisation et l'analyse de la propagation des SET au niveau transfert de registre. Par exemple, le temps de traitement et la mémoire requise sont réduits de plus de 60%. Pour la première fois, une technique basée sur les diagrammes de décision est développée pour analyser des circuits complexes, comme un multiplicateur 16 bits et des additionneurs 256 bits. D'autre part, les résultats expérimentaux démontrent que les analyses par MDP proposées sont plus rapides que les techniques contemporaines tout en assurant une meilleure précision.

## **ABSTRACT**

The exponential growth in the number of transistors per chip brought tremendous progress in the performance and the functionality of semiconductor devices associated with reduced physical dimensions and higher speed. Electronic devices used in a wide range of applications such as personal entertainment systems, automotive industry, medical electronic systems, and financial sector changed the way we live nowadays. However, recent studies reveal that further downscaling of the transistor size at nano-scale technology leads to major challenges. Reliability (i.e., ability to provide intended functionality) is one of them, where a system designed in nano-scale nodes is expected to experience more failures in its lifetime than if it was designed using larger technology node size. Such failures can lead to serious consequences ranging from financial losses to even loss of human life. Soft errors induced by radiation, which were initially considered as a rather exotic failure mechanism causing anomalies in satellites, have become one of the most challenging issues that impact the reliability of modern microelectronic systems, including devices at terrestrial altitudes. For instance, in the medical industry, soft errors have been responsible of the failure and recall of many implantable cardiac pacemakers.

Depending on the affected transistor in the design, a particle strike can manifest as a bit flip in a state element (i.e., Single Event Upset (SEU)) or temporally change the output of a combinational gate (i.e., Single Event Transients (SETs)). Initially, SEUs have been widely studied over the last three decades as they were considered to be the main source of soft errors. However, recent experiments show that with further technology downscaling, the contribution of SETs to the overall soft error rate is remarkable and in high frequency systems, it might exceed that of SEUs [1], [2]. In order to minimize the impact of soft errors, the impact of SETs needs to be modeled, predicted, and mitigated. However, despite considerable progress towards developing efficient methodologies for the functional verification of digital designs, advances in non-functional verification (e.g., soft error analysis) have been lagging. This is due to the fact that the modeling and analysis of non-functional properties related to SETs is very challenging. This can be related to the random nature of these faults and the difficulty of modeling the variation in its characteristics while propagating. Moreover, many details about the design structure and the SETs characteristics may not be available at high abstraction levels. Thus, in high level analysis, many assumptions about the SETs behavior are usually made, which impacts the accuracy of the generated results. Consequently, the lowcost detection of soft errors due to SETs is very challenging and requires more sophisticated techniques.

In this work, we present a multilevel (transistor, gate, and register transfer levels) framework to model, analyze, and estimate the soft error rate due to single event transients. The proposed framework investigates the dependencies of SET characteristics on the input pattern, propagation paths, pulse polarity, diverging paths, and re-converging paths at the transistor level. New insights on SETs propagation through different combinations of static and TSPC logic are reported. The observed behavior was then characterized to accurately model SET propagation at higher abstraction levels.

At gate level, different SET propagation techniques are developed based on formal methods and low level details extracted from transistor level analysis and the design layout. Multiway Decision Graphs (MDGs) and Satisfiability Modulo Theories (SMTs) are utilized to formally model and analyze SETs propagation. New methods to simultaneously include the impact of masking effects, width variation, and re-converging paths are developed. Reported results show that the proposed SMT modeling and analysis significantly enhances the efficiency of SET analysis in terms of: 1) accuracy as it gives accurate estimates of SET sensitivity based on gates timing extracted from layout. These results provide new insights on combinational designs vulnerability to SETs; 2) speed as it is faster than contemporary techniques; and 3) scalability as it can handle large and complex designs such as 128-bit multipliers. Moreover, based on the results of these gate level analyses, propagation tables are developed to abstract SET propagation behaviors.

At Register Transfer Level (RTL), this thesis introduces a hierarchical multi-level methodology to estimate soft error rates due to SETs in combinational designs based on formal model checking and gate level propagation tables. An RTL design is decomposed into subcomponents and then each component is annotated with its gate level details. New abstraction and design reduction methods are proposed based on the gate level propagation tables and design structure. Furthermore, two different models are proposed based on MDGs and Markov Decision Process (MDP) which are then analyzed using MDG and PRISM model checkers, respectively. Furthermore, a new method to estimate the Soft Error Rate (SER) is proposed. In order to illustrate the practical usefulness of these modeling and analysis techniques, we have analyzed different RTL combinational designs. The proposed modeling and abstraction approaches significantly reduce the time and memory requirements required to model and analyze SET propagation at RTL. For instance, the CPU time and the memory required are reduced by more than 60%. For the first time, a decision graph based technique is developed to analyze complex designs e.g., 16-bit multiplier and 256-bit adders. Moreover, experimental results demonstrate that the proposed MDP based analysis is faster than contemporary techniques, while ensuring better accuracy.

# TABLE OF CONTENTS

| DEDIC                    | ATION                                                          | III                        |

|--------------------------|----------------------------------------------------------------|----------------------------|

| ACKNO                    | OWLEDGEMENTS                                                   | IV                         |

| RÉSUM                    | ſÉ                                                             | V                          |

| ABSTR                    | ACT                                                            | ΊΙΙ                        |

| TABLE                    | OF CONTENTS                                                    | X                          |

| LIST O                   | F TABLES                                                       | ΊV                         |

| LIST O                   | F FIGURES                                                      | VI                         |

| LIST O                   | F SYMBOLS AND ABBREVIATIONS                                    | ΙX                         |

| 1.1<br>1.2               | Problem Formulation                                            | 1<br>3<br>4<br>6<br>8<br>9 |

| 1.3<br>1.4               | Thesis Contributions                                           | 9<br>10<br>11<br>13<br>14  |

| 2.1<br>2.2<br>2.3<br>2.4 | Post-Silicon Validation of SETs Using Radiation Ground Testing | 17<br>17<br>18<br>18<br>19 |

| СНАРТ                    | TER 3 BACKGROUND INFORMATION                                   | 21                         |

| 3.1        | Basics of Soft Errors due to Single Events Transients                   | 21 |

|------------|-------------------------------------------------------------------------|----|

| 3.1        |                                                                         |    |

|            | 3.1.1 Origins of Single Event Transients                                | 21 |

| 2.2        | 3.1.2 SET Masking Effects and Width Variations                          | 21 |

| 3.2        | Formal Verification Methods                                             | 22 |

|            | 3.2.1 Multiway Decision Graphs                                          | 22 |

|            | 3.2.2 MDG-Tool Set                                                      | 23 |

|            | 3.2.3 PRISM Model Checker                                               | 23 |

|            | 3.2.4 Satisfiability Modulo Theories                                    | 24 |

| 3.3        | Digital Design Flow                                                     | 24 |

| СНАРТ      | TER 4 ARTICLE 1 : NEW INSIGHTS INTO THE SINGLE EVENT TRAN-              |    |

| SIEI       | NT PROPAGATION THROUGH STATIC AND TSPC LOGIC                            | 26 |

| 4.1        | Introduction                                                            | 27 |

| 4.2        | Problem Formulation                                                     | 28 |

| 4.3        | SET Characteristics Variation in Static and TSPC Logic                  | 30 |

|            | 4.3.1 Static Logic                                                      | 30 |

|            | 4.3.2 TSPC Logic                                                        | 32 |

| 4.4        | The Impact of the Logic Structure on the SET Pulse Characteristics      | 36 |

|            | 4.4.1 Static Logic                                                      | 37 |

|            | 4.4.2 TSPC Logic                                                        | 41 |

|            | 4.4.3 Abstraction and Automation of the Proposed Analysis               | 45 |

| 4.5        | Conclusion                                                              | 47 |

| СНАРТ      | TER 5 ARTICLE 2 : MODELING, ANALYZING, AND ABSTRACTING SINGLE           | E  |

|            | ENT TRANSIENT PROPAGATION AT GATE LEVEL                                 | 49 |

| 5.1        | Introduction                                                            | 50 |

| 5.2        | Problem Formulation                                                     | 51 |

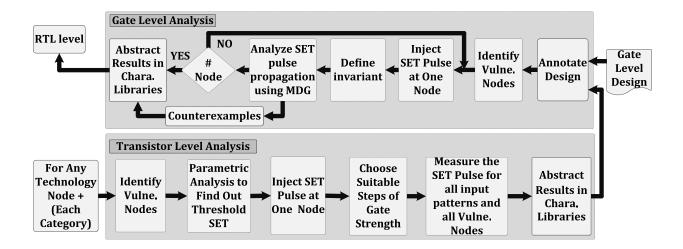

| 5.3        | Proposed Multi-level SET Pulse Propagation Analysis                     | 52 |

| 5.4        | Proposed Abstraction of SET Pulse Propagation Based on Characterization | 02 |

| 5.4        | Libraries                                                               | 52 |

| 5 E        |                                                                         |    |

| 5.5        | Gate Level Analysis of SET Pulse Propagation                            | 57 |

|            | 5.5.1 Design Annotation and SET Pulse Injection                         | 57 |

| <b>.</b> . | 5.5.2 Gate Level Analysis and Results Abstraction                       | 58 |

| 5.6        | Conclusion                                                              | 59 |

| 5.7        | Acknowledgments                                                         | 59 |

| EVI  | ENT TRANSIENTS PROPAGATION USING SMT-BASED TECHNIQUES .    | 60  |

|------|------------------------------------------------------------|-----|

| 6.1  | Introduction                                               | 61  |

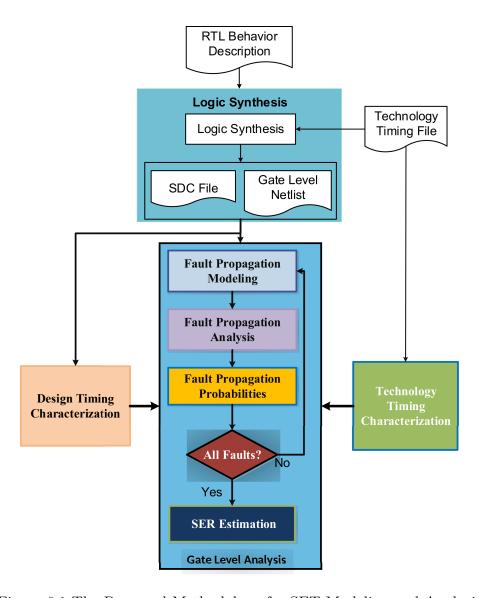

| 6.2  | Proposed Framework                                         | 64  |

|      | 6.2.1 Design Timing Characterization                       | 64  |

|      | 6.2.2 Technology Node Characterization                     | 65  |

|      | 6.2.3 Fault Propagation Modeling                           | 65  |

|      | 6.2.4 Fault Propagation Analysis                           | 69  |

| 6.3  | Experimental Results                                       | 73  |

|      | 6.3.1 SET Analysis For Multipliers                         | 75  |

| 6.4  | Conclusion                                                 | 76  |

| CHAP | TER 7 ARTICLE 4 : TOWARDS FORMAL ABSTRACTION, MODELING,    |     |

| AN   | D ANALYSIS OF SINGLE EVENT TRANSIENTS AT RTL               | 77  |

| 7.1  | Introduction                                               | 78  |

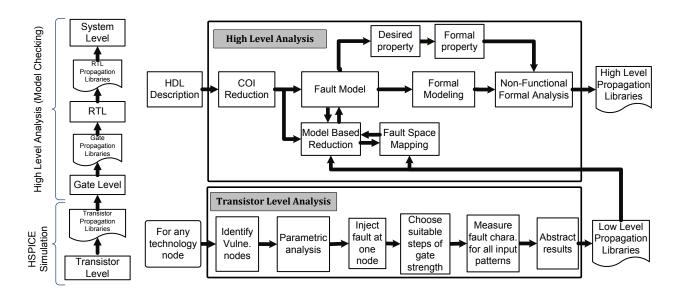

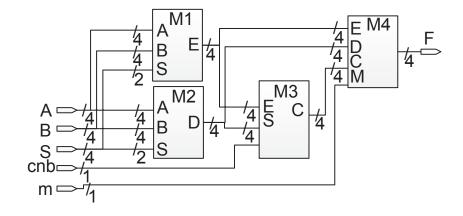

| 7.2  | Proposed Framework                                         | 79  |

|      | 7.2.1 Gate Level SET Analysis and Characterization         | 80  |

|      | 7.2.2 Abstraction of SET Propagation at RTL                | 81  |

|      | 7.2.3 Formal RTL Modeling and Analysis                     | 82  |

| 7.3  | Experiments                                                | 83  |

| 7.4  | Conclusion                                                 | 86  |

| CHAP | TER 8 ARTICLE 5 : COMPREHENSIVE MULTILEVEL PROBABILISTIC   |     |

| AN   | ALYSIS OF SINGLE EVENT TRANSIENTS PROPAGATION INDUCED SOFT |     |

| ERI  | RORS                                                       | 87  |

| 8.1  | Introduction                                               | 88  |

| 8.2  | Background and Problem Formulation                         | 91  |

|      | 8.2.1 Functional vs Non-Functional Verification            | 91  |

|      | 8.2.2 Probabilistic Model Checking & PRISM                 | 92  |

| 8.3  | Proposed Framework                                         | 92  |

|      | 8.3.1 Proposed Framework Steps                             | 93  |

|      | 8.3.2 Transistor-Level Analysis                            | 94  |

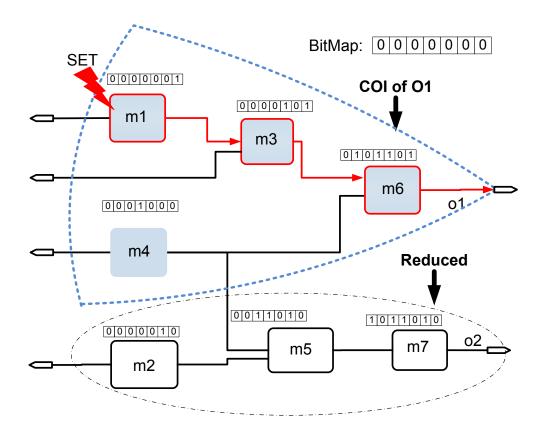

| 8.4  | High Level Design Reduction                                | 95  |

| 8.5  | High Level Formal Modeling and Analysis                    | 98  |

|      | 8.5.1 Fault Space Mapping                                  | 98  |

|      | 8.5.2 Proposed Formal Model Construction                   | 99  |

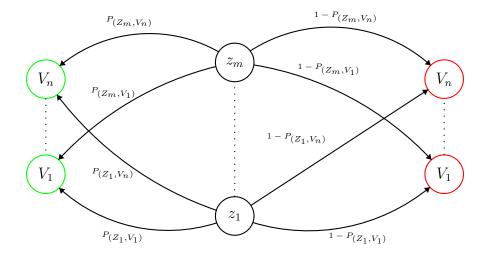

|      | 8.5.3 Proposed Markov Modeling of SET Propagation          | .01 |

|      | 8.5.4 Proposed High Level Formal Analysis                  | 03  |

| XIII  |  |

|-------|--|

| 71111 |  |

| 8.6   | Implementation of the Proposed Framework                                 | 104 |

|-------|--------------------------------------------------------------------------|-----|

|       | 8.6.1 Implementation at Gate Level                                       | 105 |

|       | 8.6.2 Implementation at RTL                                              | 109 |

| 8.7   | Discussion                                                               | 113 |

| 8.8   | Conclusion                                                               | 117 |

| СНАРТ | TER 9 GENERAL DISCUSSION                                                 | 118 |

| 9.1   | Discussion of the Proposed Transistor Level Analysis                     | 118 |

| 9.2   | Discussion of the Proposed Gate Level Analysis Methods                   | 118 |

| 9.3   | Discussion of the Proposed RTL Analysis Methods                          | 120 |

| СНАРТ | TER 10 CONCLUSION                                                        | 124 |

| 10.1  | Conclusion                                                               | 124 |

| 10.2  | Future Work Directions                                                   | 126 |

|       | 10.2.1 Layout-Based Multiple Events Transients (METs) SMT-based Analysis | 126 |

|       | 10.2.2 SMT-Based Reliability-Aware Synthesis                             | 126 |

| REFER | ENCES                                                                    | 128 |

# LIST OF TABLES

| Table 1.1 | Comparison Between High Level and Low Level Analysis                   |     |  |

|-----------|------------------------------------------------------------------------|-----|--|

| Table 4.1 | SET Pulse Propagation Through a 4-Input NAND Gate                      |     |  |

| Table 4.2 | SET Pulse Propagation Through a 4-Input NOR Gate                       | 33  |  |

| Table 4.3 | SET Pulse Generation Scenarios for the TSPC Buffer When the Cloc       |     |  |

|           | is ON                                                                  | 34  |  |

| Table 4.4 | SET Pulse Generation Scenarios for the TSPC Buffer When the Clock      |     |  |

|           | is OFF                                                                 | 35  |  |

| Table 4.5 | The Dependence of the SET Pulse Amplitude on the Particle Strike       |     |  |

|           | Time for the TSPC Buffer                                               | 36  |  |

| Table 4.6 | Analysis of the SET Pulse Characteristics Variation Due to the Strike  |     |  |

|           | Time for the Scenarios in Table 4.5                                    | 37  |  |

| Table 4.7 | The Effect of the Re-converging Paths on the PIPB                      | 41  |  |

| Table 4.8 | Abstraction of the SET Pulse Propagation Induced Byzantine Fault       |     |  |

|           | Scenarios                                                              | 44  |  |

| Table 4.9 | Abstraction of the SET Byzantine Pulse Re-converging Propagation       |     |  |

|           | Scenario for 2-Input TSPC OR Gate                                      | 46  |  |

| Table 5.1 | The Characterization Library of the C17                                | 56  |  |

| Table 5.2 | Analyzed Benchmark Circuits                                            | 58  |  |

| Table 6.1 | Comparison of Processing Times to Estimate SERs Between our Fra-       |     |  |

|           | mework and Contemporary Techniques for ISCAS85 Benchmarks              | 74  |  |

| Table 6.2 | Comparison of SER Analysis Times for Different Multipliers with State- |     |  |

|           | of-the-art Methods.                                                    | 76  |  |

| Table 7.1 | Results of our Gate Level Analysis of a Full Adder                     | 80  |  |

| Table 7.2 | Benchmark Circuits Characterized at Gate Level                         | 81  |  |

| Table 7.3 | The Verification of SET Pulse Propagation for Multipliers 8            |     |  |

| Table 8.1 | Comparison Between High Level and Low Level Analysis                   | 92  |  |

| Table 8.2 | Comparison Between the Proposed Framework and the Contemporary         |     |  |

|           | Techniques                                                             | 100 |  |

| Table 8.3 | Illustrative Example for the Difference Between Modeling SET Propa-    |     |  |

|           | gation as MDP and DTMC                                                 | 103 |  |

| Table 8.4 | Characterized Benchmark Circuits at Gate Level                         | 108 |  |

| Table 8.5 | SET Propagation Probabilities for Full Adder                           |     |  |

| Table 8.6 | Propagation Probabilities for a 4-bit ALU Circuit                      | 114 |  |

| Table 8.7 | Comparison Between the Proposed Framework and the Contemporary     |     |  |

|-----------|--------------------------------------------------------------------|-----|--|

|           | Techniques at Gate Level                                           | 115 |  |

| Table 8.8 | Digital Designs Analyzed at RTL                                    | 117 |  |

| Table 9.1 | Detailed Comparison Between the SET Gate Level Analysis Techniques |     |  |

|           | Proposed in This Thesis                                            | 120 |  |

| Table 9.2 | Detailed Comparison Between the SET RTL Analysis Techniques Pro-   |     |  |

|           | posed in This Thesis                                               | 122 |  |

# LIST OF FIGURES

| Figure 1.1  | The Digital Design Flow                                                  | 6  |  |

|-------------|--------------------------------------------------------------------------|----|--|

| Figure 1.2  | The Concept of Modeling SET Propagation at High Levels Based on          |    |  |

|             | the Observed Behavior at Low Level                                       | 7  |  |

| Figure 1.3  | The Concept of Cross-Layer Modeling and Analysis of SET Prorogation      | 8  |  |

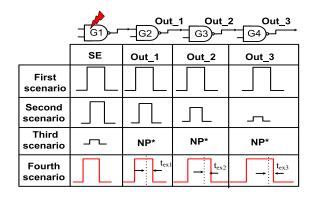

| Figure 3.1  | Different Scenarios for SET Pulse Propagation. (*NP Means SET Pulse      |    |  |

|             | is Not Propagating)                                                      | 22 |  |

| Figure 4.1  | CMOS Transistor Level Implementation of (a)- a 4-Input NAND Gate,        |    |  |

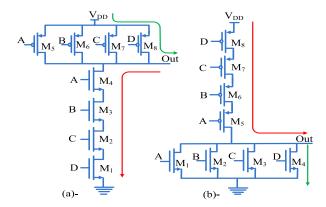

|             | (b)- a 4-Input NOR Gate                                                  | 31 |  |

| Figure 4.2  | Transistor level schematic of TSPC buffer gate (split output implemen-   |    |  |

|             | tation). (a) Positive latch (b) Negative latch                           | 33 |  |

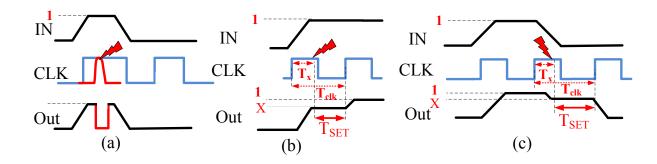

| Figure 4.3  | SET Pulse Width Variations Due to the Strike Time for the Scenario       |    |  |

|             | Shown in the 2nd Row of Table 4.3                                        | 35 |  |

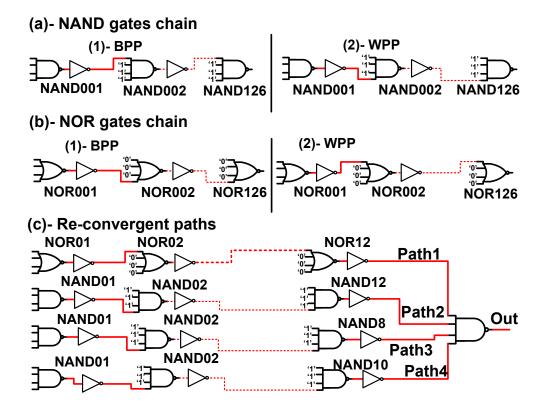

| Figure 4.4  | Schematic Description of the Chain of the NAND and NOR Gates.            |    |  |

|             | (a)- the BPP and the WPP for the NAND Gates Chain (b)- the BPP           |    |  |

|             | and the WPP for the NOR Gates Chain (c)- the Re-converging Path          |    |  |

|             | Combinational Design                                                     | 38 |  |

| Figure 4.5  | The WPP and the BPP for the NAND and NOR Gates Chain. Measu-             |    |  |

|             | red SET Pulse Width Versus the Strike Node Along the NAND Gates          |    |  |

|             | Chain. The Chain Supply Voltage 1.2 $\it{V}$ . The Input SET Pulse Width |    |  |

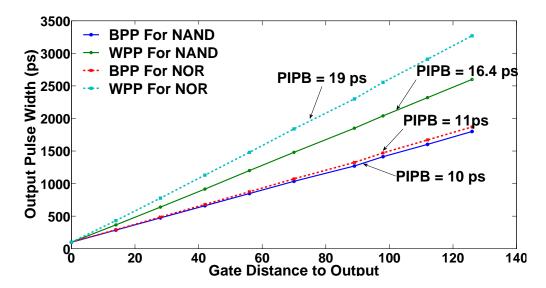

|             | is 100 ps                                                                | 39 |  |

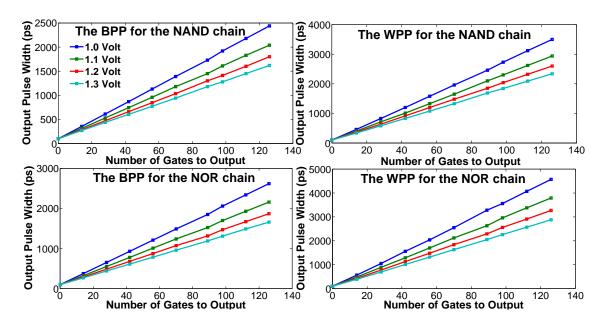

| Figure 4.6  | Measured SET Pulse Width Versus the Strike Position Along the NAND       |    |  |

|             | and the NOR Gates Chains When the Supply Voltage Varies From 1           |    |  |

|             | V to 1.3 $V$ and the Initial SET Pulse Width is 100 $ps$                 | 40 |  |

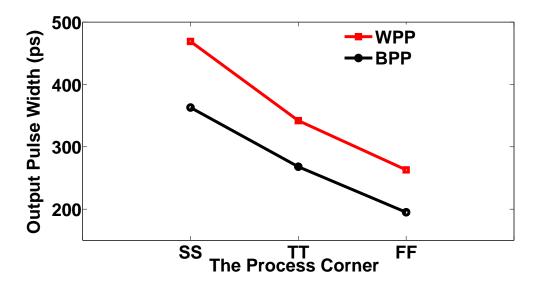

| Figure 4.7  | Simulation Results for the Best and Worst Propagation Path Among         |    |  |

|             | Different Corners for a Chain of 14 NAND Gates                           | 40 |  |

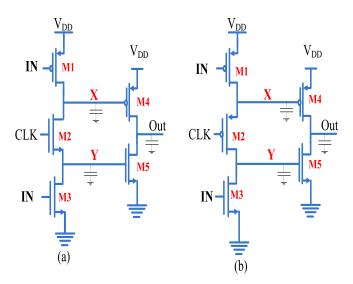

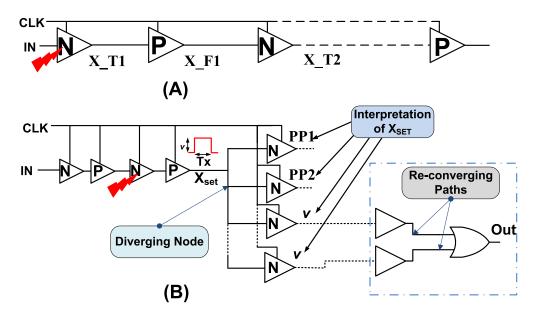

| Figure 4.8  | Schematic Description of the Combination of the TSPC Logic. (a)-         |    |  |

|             | Chain of Alternative N-block and P-block of TSPC Buffers, (b)- Di-       |    |  |

|             | verging and Re-converging Paths                                          | 43 |  |

| Figure 4.9  | Simulation Results of the SET Pulse Propagation Through a Chain of       |    |  |

|             | TSPC Buffers Shown in Fig. 4.8(a)                                        | 43 |  |

| Figure 4.10 | Variation in the Width of SET Pulses While Propagating Through a         |    |  |

|             | Chain of TSPC Buffer                                                     | 44 |  |

| Figure 4.11                                                               | The Variation in the Amplitude of the SET Pulse While Propagating      |    |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|----|

|                                                                           | Through a Chain of TSPC Buffers                                        | 44 |

| Figure 4.12 General Steps of a Possible Automated SET Pulse Propagation A |                                                                        | 46 |

| Figure 5.1                                                                | 5.1 General Steps of our Proposed Methodology of SET Pulse Propagation |    |

|                                                                           | Analysis at Transistor and Gate Level                                  | 52 |

| Figure 5.2 Characterization Libraries of Both NAND and NOR Gates          |                                                                        | 53 |

| Figure 5.3                                                                | Characterization Library Modeling of a Re-convergent Gate              | 54 |

| Figure 5.4                                                                | (a) SET Pulse Propagation Induced Byzantine Fault in Static Logic.     |    |

|                                                                           | (b) Abstraction of SET Pulse Propagation Induced Byzantine Fault       |    |

|                                                                           | Scenarios                                                              | 55 |

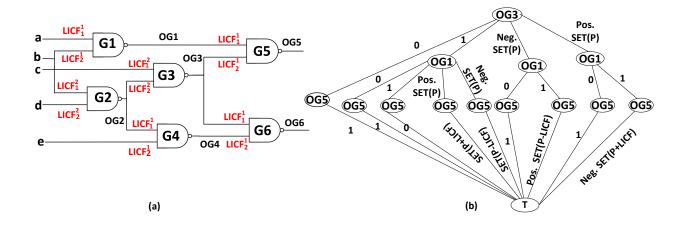

| Figure 5.5                                                                | (a) The Annotated C17 Design With the LICF Values, (b) Multiway        |    |

|                                                                           | Decision Graph (MDG) for G5 From the C17 Design                        | 55 |

| Figure 5.6                                                                | The Use of the Characterization Library at the RTL                     | 57 |

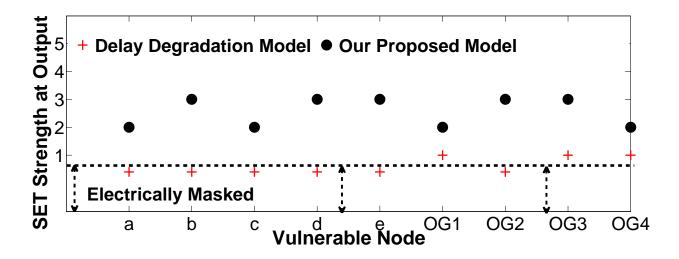

| Figure 5.7                                                                | The SET Pulse Propagation Based on the Delay Degradation Model         |    |

|                                                                           | (DDM) [3] Versus our Proposed Model                                    | 59 |

| Figure 6.1                                                                | The Proposed Methodology for SET Modeling and Analysis                 | 63 |

| Figure 6.2                                                                | Modeling of Combinational Designs                                      | 67 |

| Figure 6.3                                                                | Proposed Characterization of Re-converging SETs                        | 69 |

| Figure 6.4                                                                | An Example on the SET Re-converging Scenarios                          | 70 |

| Figure 6.5                                                                | The Relationship Between SER and SET Width                             | 74 |

| Figure 7.1                                                                | Steps of the Proposed Framework for the Investigation of SET Propa-    |    |

|                                                                           | gation at Gate and RTL Levels                                          | 79 |

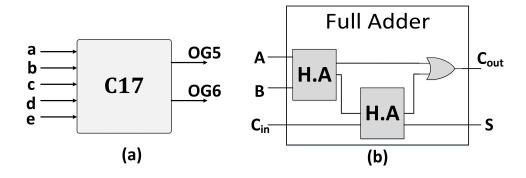

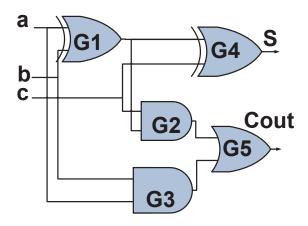

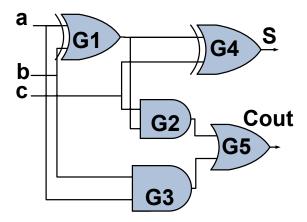

| Figure 7.2                                                                | Gate Level Model of a Full Adder                                       | 81 |

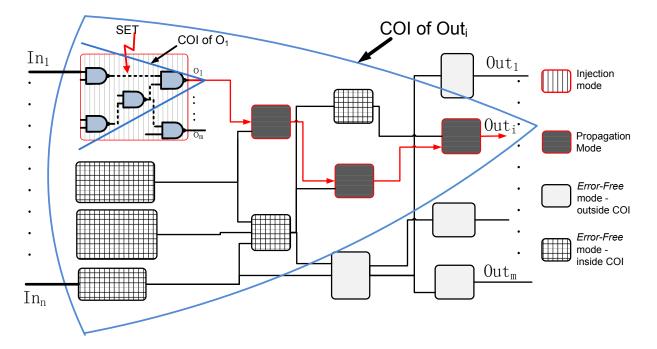

| Figure 7.3                                                                | Decomposing an RTL Design and Deciding the Mode of Operation of        |    |

|                                                                           | its Sub-components Based on the Injection Scenario                     | 82 |

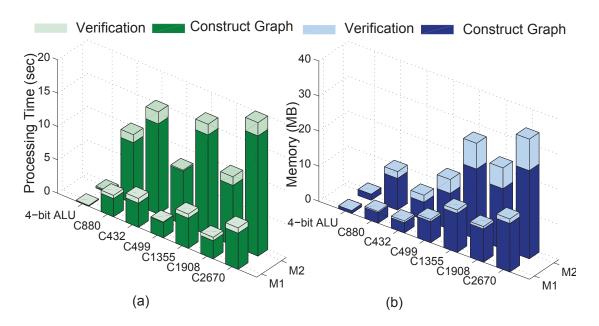

| Figure 7.4                                                                | RTL Analysis of Combinational RTL Design, $M1$ is Our Proposed Fra-    |    |

|                                                                           | mework and $M2$ is the $Boolean$ Method. (a) Comparison Between $M1$   |    |

|                                                                           | and $M2$ for the Processing Time. (b) Comparison Between $M1$ and $M2$ |    |

|                                                                           | for the Memory Requirements                                            | 84 |

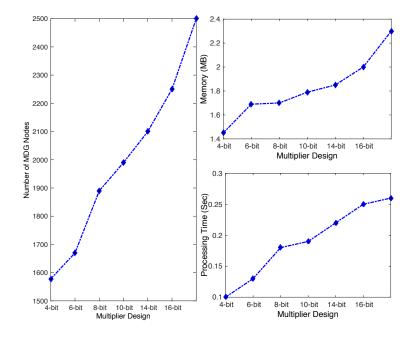

| Figure 7.5                                                                | The Variation in the Average Processing Time, Memory, and Number       |    |

|                                                                           | of Decision Graph Nodes Required to Construct the MDG Graph and        |    |

|                                                                           | Analyze SET Propagation for one Injection Scenario                     | 85 |

| Figure 8.1                                                                | The Proposed Multi-Level Framework for Modeling and Investigating      |    |

|                                                                           | Fault Propagation                                                      | 93 |

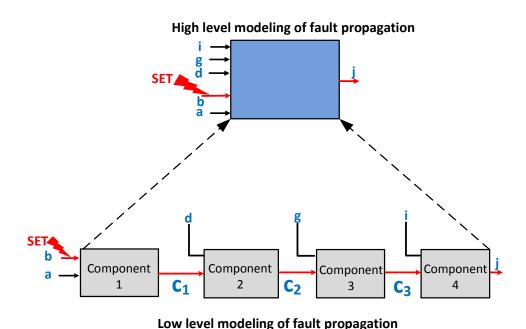

| Figure 8.2                                                                | The Concept of Modeling SET Propagation at High Level Based on         |    |

|                                                                           | Low Level Propagation Details                                          | 94 |

| Figure 8.3  | COI and Model Based Reduction                                                   |     |  |

|-------------|---------------------------------------------------------------------------------|-----|--|

| Figure 8.4  | Fault Tree of our Proposed Fault Space Mapping                                  | 98  |  |

| Figure 8.5  | Comparison Between the Proposed Framework and the Contemporary                  |     |  |

|             | Techniques                                                                      | 99  |  |

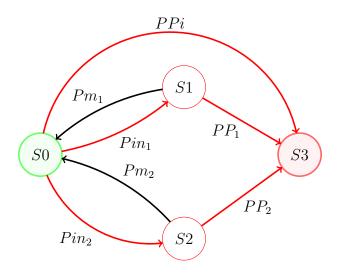

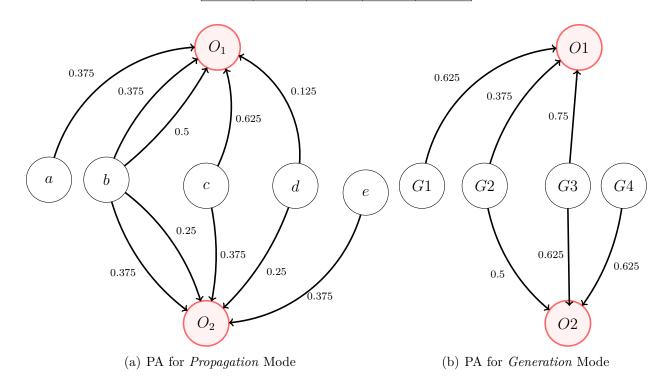

| Figure 8.6  | General Probabilistic Automata for any Component                                |     |  |

| Figure 8.7  | Illustrative Example for the Difference Between Modeling SET Propa-             |     |  |

|             | gation as MDP and DTMC                                                          | 102 |  |

| Figure 8.8  | Annotated Gate Level Model of C17 (ISCAS85 Benchmark) Design.                   | 105 |  |

| Figure 8.9  | Probabilistic Model of SET Propagation Through a 2-input NAND                   |     |  |

|             | Gate. $PP_i$ is the Injection Probability for a NAND gate. $PP_1$ and $PP_2$    |     |  |

|             | are the Propagation Probabilities for an SET Propagating Through $in_1$         |     |  |

|             | and $in_2$ , Respectively. $Pin_1$ and $Pin_2$ are the Probabilities an SET is  |     |  |

|             | Reaching $in_1$ and $in_2$ , Respectively. $Pm_1$ and $Pm_2$ are the Probabili- |     |  |

|             | ties That an SET is Masked While Propagating Through $in_1$ and $in_2$ ,        |     |  |

|             | Respectively.                                                                   | 106 |  |

| Figure 8.10 | Utilizing the Gate Level Table to Construct the Probabilistic Automata          |     |  |

|             | for SET Propagation for the C17 Benchmark Design                                | 108 |  |

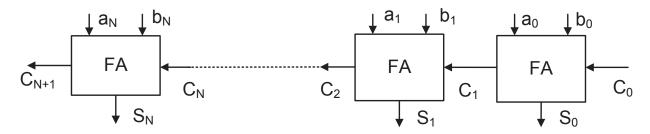

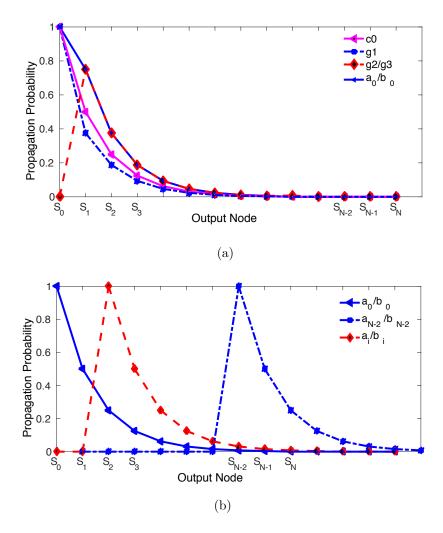

| Figure 8.11 | RTL of N-bit RCA and its SET Propagation Probabilities                          | 109 |  |

| Figure 8.12 | Gate Level Structure of the Analyzed Full Adder                                 |     |  |

| Figure 8.13 | Modeling of SETs Propagation Probabilities in a N-bit RCA at RTL                |     |  |

|             | Based on the Injection Scenario                                                 | 111 |  |

| Figure 8.14 | The Results of the RTL Analysis of SET Propagation Probabilities of             |     |  |

|             | a N-bit RCA                                                                     | 112 |  |

| Figure 8.15 | RTL Structural of the 4-bit ALU Circuit                                         | 112 |  |

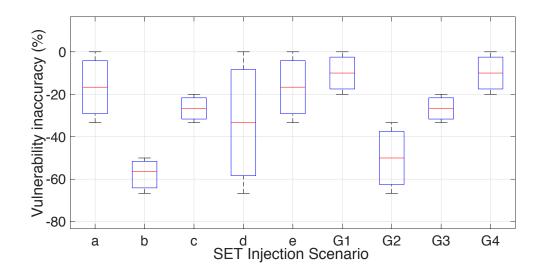

| Figure 8.16 | Inaccuracy in the Evaluation of the SET Propagation Probabilities in            |     |  |

|             | Related Works [4, 5] for the C17 Benchmark                                      | 113 |  |

| Figure 8.17 | Inaccuracy in the Evaluation of the SET Propagation Probabilities in            |     |  |

|             | Related Works [6, 4] by Relying Only on the Gate Level CICs for the             |     |  |

|             | 4-bit ALU Circuit                                                               | 116 |  |

# LIST OF SYMBOLS AND ABBREVIATIONS

ADD Algebraic Decision Diagram

ASM Abstract State Machine BDD Binary Decision Diagram

BD Bundle Data

DAG Directed Acyclic Graph

DI Delay Insensitive FOL First Order Logic

MDG Multiway Decision Graph

ROBDD Reduced Order Binary Decision Diagram

SEE Single Event Effects

SET Single Event Transient

SEU Single Event Upset

SER Soft Error Rate

SRAM Static Random-Access Memory

SMT Satisfiability Modulo Theory

EDA Electronic Design Automation

PMC Probabilistic Model Checking

FT Fault Tree

RTL Register Transfer Level

TPT Transistor Propagation Table

CIC Critical Input Combination

CMOS Complementary metal-oxide-semiconductor

COI Cone Of Influence

WOV Window Of Vulnerability

TSPC True Single Phase Clock

PIPB Propagation Induced Pulse Broadening

# CHAPTER 1 INTRODUCTION

Aggressive technology downscaling has enabled a remarkable improvement of integrated circuits (ICs) performance, power consumption and cost over the past five decades. This evolution made the integrated circuits indispensable part of our daily lives. However, nanometer technology scale has brought into attention reliability issues that were previously not as much of a concern. This is mainly because it is becoming harder to guarantee the correct functionality of integrated circuits in various environments and design configurations. There are three main sources of unreliability in nanoscale designs namely; runtime variations (e.g., transistor aging degrade), process variations (e.g., variation in the transistor size), and external radiation-induced soft errors. Process variations are naturally occurring variations in the attributes of transistors (length, widths, oxide thickness) when integrated circuits are fabricated. The unreliability induced by process variations and runtime variations can change cells delay and might eventually impact the timing of a system. Designers working at circuit level usually account for such phenomena by introducing additional timing margins (i.e., relaxing the design timing requirements).

On the other hand, the unexpected behaviors introduced in a system due to external radiationinduced soft errors are much harder to mitigate. This is mainly because such faults have a random nature. In other words, soft errors impact the design behavior for very short periods of time, then they disappear and it is very hard to reproduce and relocate them. For instance, they were responsible for the catastrophic failure and the recall of many safety critical systems, such as implantable cardiac pacemakers [7]. Furthermore, developing low-cost analysis and mitigation techniques for soft errors is very challenging and require novel methods and tools. As a result, soft errors have become one of the most challenging types of uncertainties that impact the reliability of modern electronic systems. These errors are the results of an external hit by a radiation-induced particle when striking the sensitive area of a transistor. For example, an alpha particle in packaging material or neutron particle from cosmic rays. These external radiations, if they have the required strength, can change the output of a transistor for a very short period of time. Depending on the affected transistor, it might flip the value stored in a state element (called as Single Event Upset (SEU)) or temporarily change the output of a combinational gate (known as a Single Event Transients (SETs)). Initially, SEUs have been widely studied over the last three decades as they were considered to be the main source of soft errors. However, with further technology downscaling, SETs have become a major source of soft errors in digital circuits. This is mainly because with each new technology node, a sufficient change in the error generation and propagation behavior is

observed. According to recent studies, smaller device geometries, large number of transistors, and the requirement of a high speed design allow particles with smaller energy to generate SETs and eventually cause a soft error [8], [9]. The sensitivity of integrated circuits to soft errors has grown significantly over the past decade. As a result, there is a growing need to analyze and estimate the impact of soft errors on today's complex digital designs as early as possible in the digital design cycle. The purpose of such analysis is to guide the design and the development of circuits that can tolerate soft errors due to SETs in cost and power effective manner. In other words, in order to achieve cost-efficient reliable integrated circuits, it is crucial to take the reliability into consideration alongside with the conventional area, power, and performance metrics in the design flow.

The rest of this chapter is organized as follows. Section 1.1 identifies and provides evidence of the problem we are addressing in this thesis. In this section, the main limitations of existing modeling and analysis techniques at different abstraction levels are summarized. Moreover, in this section, we introduce both the concept of multilevel and cross layer modeling and analysis which will be used through this thesis. Thereafter, in Section 1.2, the main objectives of this thesis are identified in order to advance this area of research. The main contributions presented in this thesis are summarized in Section 1.3.

#### 1.1 Problem Formulation

Soft errors, induced by radiation, are an increasingly relevant issue impacting the reliability of CMOS Integrated Circuits (ICs) adopted not only in safety-critical applications, such as space and avionic, but also in ground-level applications [10], [11]. The progressive shrinking of device sizes in advanced processing technologies, which have scaled from  $0.5~\mu m$  to 32~nm in less than two decades, leads to miniaturization and performance improvements. However, the possibility of Single Event Transients (SETs) generation, when an energetic particle hits one of the sensitive sites of a digital circuit, has significantly increased in modern Deep Sub-Micron (DSM) technologies. Therefore, ultra-deep sub-micron technologies are more vulnerable to soft errors [10]. Hence, there is a growing need for fast, accurate, and efficient analysis and estimation techniques of SET propagation in modern-DSM technologies. Contemporary techniques for analyzing SET propagation can broadly be classified based on the level of abstraction at which the analysis is performed: at low or at high abstraction level.

## 1.1.1 Analysis of SETs at Low Levels

At the transistor level, SET propagation is analyzed using both circuit simulations and experimental analysis. Using simulation based techniques, SET propagation scenarios have been investigated in [3], [12], [13], [14]. Moreover, the impact of technology downscaling on SET characteristics variation while propagating has been analyzed in [15], [16]. Similar analyses of the impact of technology scaling on SET characteristics have been done using both mixed-mode simulations [17] and experimental measurements [18]. SET propagation has been modeled in [19], [20], [21] as a function of the technology, gate design and bias history. Further SET studies showed combined effects, such as temperature [22], [23], and technology [24]. Experiments were also performed to characterize SET sensitivity of new technologies using broad beams of heavy ions [25], [26], [27], [28], [29].

However, contemporary techniques which analyze SET propagation at this level suffer from the following shortcomings:

- 1. Detailed transistor level analysis to investigate the impact of the following factors on SET characteristics while propagating in digital designs is missing:

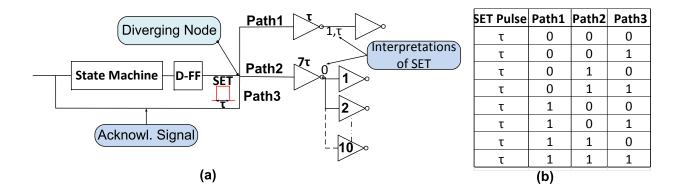

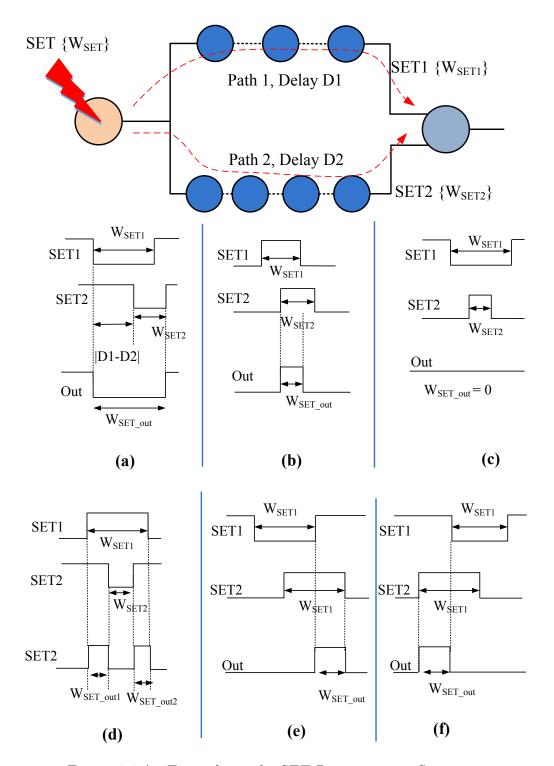

- Diverging and re-converging paths: SET propagation through a diverging node can lead to multiple faults at different primary outputs. Moreover, due to reconverging paths, the width of SETs, which propagate through different paths between the fault striking node and the re-converging gate, may combine or overlap when arriving simultaneously at the input of a re-converging gate. Performing such analysis by circuit simulation is possible on small circuits but becomes intractable in large digital systems.

- Input pattern and SET polarity: the variation of the propagation delay for different input patterns of multiple inputs static gates is well known to the community ([30], Chapter 6). Hence, it is possible that SET width in a static gate varies for different input patterns. Moreover, the variation in SET characteristics might be dependent to its polarity.

- Timing constraints: in the True Single-Phase-Clocked (TSPC) logic, the characteristics of SET may vary due to the particle strike time and the timing conditions of the gate where SET propagates through. The impact of all these timing constraints on SET characteristics need to be characterized. Moreover, SET generation and propagation in TSPC logic have not been fully analyzed. This logic was first proposed to deal with the skew problem in the dynamic logic, such as clocked CMOS [31], domino [32], and NORA logic [33]. In TSPC logic, it is possible to achieve high clock frequencies because it simplifies the clock distribution and eliminates

phase overlapping problems [34, 35, 36, 37]. Different possible implementations for the TSPC logic, which use low number of transistor, have been presented in [35]. Furthermore, TSPC logic has been used to develop high operating frequency dividers, and to reduce the power dissipation [38, 39].

2. Several simulation based techniques and tools to estimate the SER using the Monte Carlo method at the transistor level have been proposed, such as SEMM [40]. The accuracy of these techniques is directly related to the number of simulation runs. In addition, Monte Carlo techniques introduce randomness in the simulations and fail to cover all possible scenarios. Mixed-mode simulations [17] reduce the simulation time required by a static approach using a mixed-mode simulator, where the current injection part is simulated at the circuit level, while the rest of the circuit can be modeled at the timing level. Moreover, in order to reduce the overhead of detailed circuit simulations, a combination of analytic and simulation based methods to estimate the SER has been implemented in different tools, such as SERA [41] and SEUPER\_FAST [42]. However, simulation based techniques are very time consuming when dealing with large systems and require a large amount of resources.

## 1.1.2 Analysis of SETs at Higher Abstraction Levels

As designs in modern DSM are more vulnerable to soft errors, it has become imperative to address SET propagation issues at an earlier stage in the design flow. Therefore, researchers came up with different SET propagation models operating at gate and higher abstraction levels. Some of these techniques are also based on simulations with fault injection based on random vector generation [43], [44]. Moreover, several Monte Carlo simulation based techniques have been proposed to analyze the impacts of the masking effects (logical, electrical, and timing masking) on SET propagation at gate level, such as [45], [46], [47].

Other research groups have addressed this issue using formal verification methods such as; Binary Decision Diagram (BDD)-based techniques [48], a combination of Reduced-Order Binary Decision Diagrams (ROBDDs) and Algebraic Decision Diagrams (ADDs) [49], and Boolean satisfiability solvers (SAT-solvers) [6]. However, contemporary techniques at gate and higher levels suffer from the following shortcomings:

1. Several simulation based techniques have been proposed to estimate the SER in combinational logic at gate and higher abstraction level. At gate level, tools, such as FAST [45], ASERTA [46], and ASSA [47], have been proposed to analyze the impact of all masking effects on SET characteristics. These tools use a zero-delay fault simulator to analyze logical masking. Moreover, these tools have different implementations of the

delay degradation model due to electrical masking, which was proposed in [3]. The model in [3] uses look up tables and an equivalent inverters chain based approach. However, all the aforementioned tools are not able to correctly predict the behavior of asynchronous circuits. Such techniques can only handle combinational and synchronous sequential circuits. Additionally, simulation based approaches have serious shortcomings as they can be very time consuming for large designs with many primary inputs and sequential states. Furthermore, these techniques have their drawbacks in terms of accuracy. This is mainly because the accuracy of fault simulation decreases with the ratio of the simulated sample size over the total vector space size.

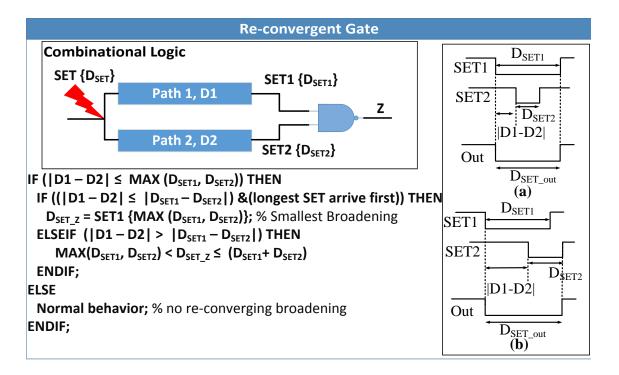

Different numerical techniques are proposed, such as [50], [51], [52] [41]. Each of these techniques try to estimate the impact of masking effects on the SER. Electrical masking is presented in [50], temporal masking is analyzed in [41], and a model combining all masking effects is presented in [51]. However, these techniques are not scalable and their models do not include the impact of SET broadening and SET re-convergence.

- 2. State-of-the-art techniques at gate level (such as [48], [49]) analyze the susceptibility of digital circuits to soft errors by modeling only the masking effects that can prevent SET in digital designs from propagating [10]. These techniques omit the possibility that a SET could broaden while propagating. SET broadening was first observed in [53] and it has recently gained more attention and was addressed in [12, 54, 20, 55]. Furthermore, at Register Transfer Level (RTL), many details related to the design structure and SET characteristics are not available. Therefore, in [6, 56], SETs are modeled at RTL as bit flips. Thus, the SER estimated at this abstraction level is generally inaccurate.

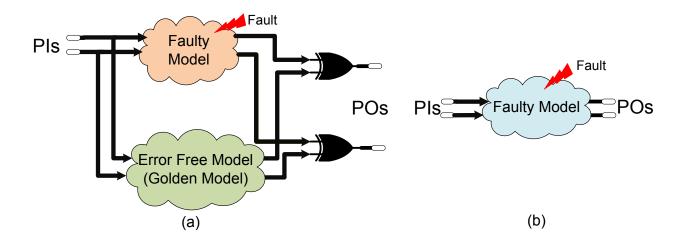

- 3. Techniques based on contemporary formal verification are resource hungry and suffer from a state explosion problem. This is mainly due to the intrinsic characteristics of their SET modeling technique. Indeed, in these techniques, each input vector is mapped to a unique state. Therefore, the corresponding Markov model has 2<sup>M</sup> states (M primary inputs). Additionally, with these techniques, the formal model of the design size is doubled due to the requirement of two design versions, mainly a golden and a faulty version. For each injection scenario, in order to determine if a SET is propagating, the outputs of both the golden and the faulty version are compared. With such modeling technique, any formal tool rapidly runs out of memory, even when trying to analyze moderate size designs e.g., a 14-bit adder [56].

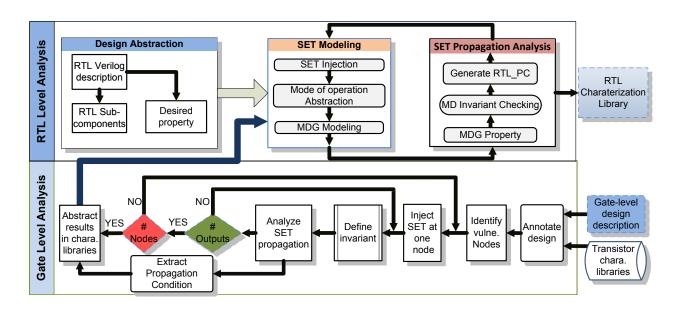

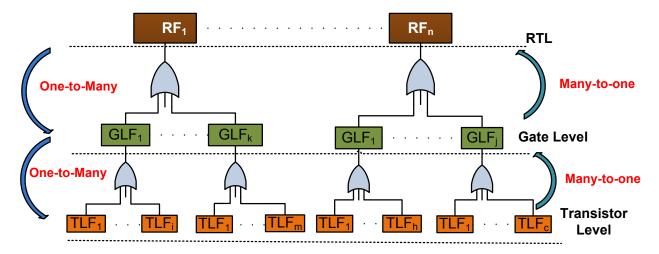

## 1.1.3 Multi-level Modeling and Analysis of SET Propagation

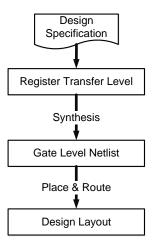

Designers and researchers found that the best way to build complex hardware designs is to start from very high level descriptions and synthesize them all the way down to layout as shown in Fig. 1.1. This methodology is only applicable to synthesizable designs. With synthesis, the code representing the design at one abstraction level can be translated into lower level implementations using pre-characterized rules and libraries. In other words, a design is synthesizable if the synthesis tool has the synthesis library (i.e., from which the low level implementation can be generated) for each part of the design. Therefore, the main concept in the design methodology is to utilize the lower level details from pre-characterized data to build large designs. In each synthesis phase between two abstraction levels, more details about the design structure are added.

Figure 1.1 The Digital Design Flow.

Unfortunately, when it comes to non-functional design verification, it is totally different and there is no unified approach. Design verification at one abstraction level relies on the information provided at this level. As shown in Table 8.1, low level analysis is very detailed, however, it is resource consuming and not applicable for large designs. On the other hand, higher level analyses are more time and resource efficient. However, their results have limited accuracy and do not provide much useful information to the designers about the design behavior in presence of different kinds of uncertainties. Therefore, there is a growing need to reduce the gap between the fault analyses at these different abstraction levels.

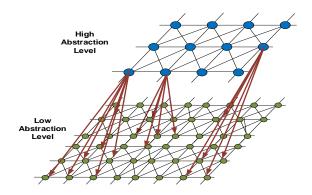

In order to visualize this issue, consider Fig. 1.2. At each abstraction level, there is a number of faults (represented in Fig. 1.2 as dots) which can lead to design failures. Each of these faults are triggered by a number of faults from lower abstraction levels. Thus, if the details of faults from lower abstraction levels are available, then it is possible to accurately model and analyze

them at higher abstraction levels. Verification engineers define possible fault candidates based on the amount of details available about the design structure at one abstraction level. The number of faults in the design increases as we are moving toward lower abstraction levels. However, faults at one abstraction level do not have the same weight, i.e., possibility of occurrence.

To overcome this issue, the usability of the results of the fault analysis at each abstraction level has to be improved. New methods to abstract the design details that directly affect fault propagation are required. However, we have to ensure that the additional overheads in terms of learning and verification are reasonable.

Figure 1.2 The Concept of Modeling SET Propagation at High Levels Based on the Observed Behavior at Low Level

Table 1.1 Comparison Between High Level and Low Level Analysis

|                  | Analysis at Gate<br>and Higher Level | Analysis at Transistor<br>and lower Level |

|------------------|--------------------------------------|-------------------------------------------|

| Fault Modeling   | Very Abstract                        | Very Detailed                             |

| Accuracy         | does not reflect                     | Reflects actual                           |

|                  | actual fault behavior                | behavior                                  |

| Complexity       | Less Complex                         | Very Complex                              |

| Result's         | Under/Over                           | More                                      |

| Accuracy         | estimation                           | accurate                                  |

| Result's         | Not                                  | Not                                       |

| Usability        | used                                 | used                                      |

| Memory           | Less Memory                          | High Memory                               |

| CPU Verification | Less                                 | Very Large                                |

| Time             | Time                                 | Time                                      |

## 1.1.4 Cross layer Modeling and Analysis of SET Propagation

In order to perform an accurate SET analysis, details from the circuit level are required. At circuit level, parameters extraction and detailed simulations can provide a certain level of accuracy for phenomena such as electrical masking and SET width variation. However, this analysis is very computationally intensive and would be intractable at the chip level and is only tractable at the cell level. In other words, this type of analysis can be conducted on hundreds of transistors at most. Similar to functional verification, existing SET analysis techniques abstract the design details to perform such analysis at higher abstraction levels (i.e., gate level or higher). However, abstraction normally comes at the cost of reduced accuracy, since many details about the design layout and the SET's characteristics are abstracted. Therefore, a new technique which satisfies the following requirements is needed: 1) to be fast; 2) to be more scalable than circuit level analysis; and 3) to be able to model SET propagation based on underlying technology details to maintain a certain level of accuracy.

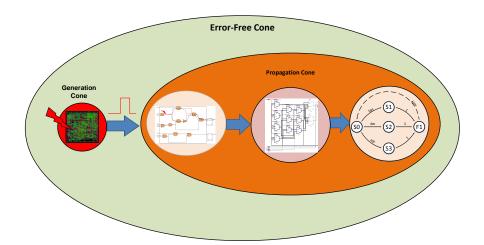

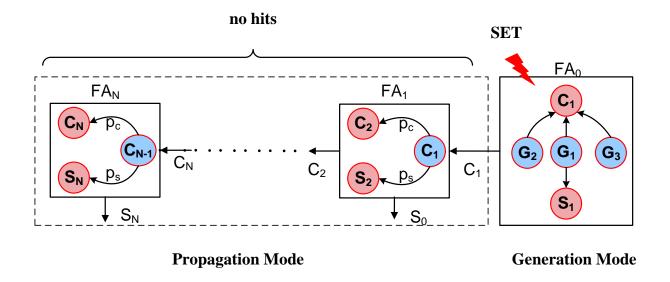

As explained before, single event transients start at the device level (at some sensitive area of the transistor) and can propagate to impair the behavior of a whole system. Therefore, one possible idea is to model each component of a design based on its relation with the injected SET into the following classes: 1) the component that was affected by radiation and an SET generated internally in this component; 2) the components that propagate the generated SET from where it is injected to one or more primary output; and 3) the components which do not generate nor propagate SETs i.e., Error-Free.

Figure 1.3 The Concept of Cross-Layer Modeling and Analysis of SET Prorogation

Based on this classification, for each injection scenario, a design can be divided into three cones: a) Generation cone; b) Propagation Cone; and c) Error-Free Cone as shown in Fig.

1.3. As depicted in this figure, the *Generation cone* is expected to be small in size, but contains more details. On the other hand, the propagation cone can be very large in size, but it contains reduced amount of details (i.e., its accurate modeling is less expensive). In the propagation cone, we can have different sub cones where each has certain amount of details based on SET propagation behavior in this sub-cone (see Fig. 1.3). The *Error-Free Cone* includes all the Error free components which do not directly propagate the SET but they might impact its propagation (by enabling or blocking some paths or by loading other paths). Later in this thesis, this idea of modeling and analyzing the SET propagation using variable levels of details for different regions in a cross-level approach is investigated in details.

### 1.2 Thesis Objectives

Based on the previous discussions of the limitations in the existing SET modeling methods, it can be noticed that the following important questions are not appropriately addressed in the literature so far:

- **R1**: What is the impact of the propagation paths, polarity, and fanout re-convergence on SET characteristics?

- **R2**: How to abstract the SET propagation behavior observed at transistor level at higher abstraction levels?

Based on our discussions of existing SET propagation modeling at higher abstraction levels (i.e., gate level and higher) it can be noticed that the following important questions are not appropriately addressed in the literature so far:

- R3: How to improve the usability of the results generated from lower abstraction levels such as transistor level analysis?

- **R4**: How to efficiently utilize formal verification methods to model and analyze SET propagation at high abstraction level?

- R5: How to measure the vulnerability of complex designs at high abstraction levels without losing the accuracy provided from low level analysis?

- R6: Is it possible to improve scalability while preserving accuracy?

Our objective in this thesis is to investigate possible solutions to the questions introduced in this section at transistor, gate, and register transfer levels.

#### 1.3 Thesis Contributions

In this thesis, I developed a multilevel framework which accurately models and analyze soft errors in digital circuit due to single event transients from a technology response model derived at the transistor level all the way to the register transfer level. At each abstraction level, suitable modeling of phenomena related to SET propagation are proposed. Formal verification methods are utilized at the higher abstraction level to build an accurate exhaustive modeling. Moreover, new quantitative measures of the contribution of SETs at each node in the design to the design failure are proposed. Furthermore, in the proposed analysis at each abstraction level, new means of estimating the soft error rate are proposed. The rest of this section summarizes the main contributions developed in this thesis.

# 1.3.1 Transistor Level Analysis of SET Propagation

I conducted different analyses to fully understand SET propagation behavior at the transistor level and to address the research question reported in Section 1.2 (i.e., R1 and R2). I have analyzed SET characteristics variation while propagating through both static and TSPC logic at the transistor level. This work is distinct in the following ways:

- 1. Investigate the impact of propagation path on SET (related to R1): The variations in SET characteristics based on the characteristics of its propagation paths are investigated. SET width broadening or attenuation based on the propagation paths are characterized. Worst and best propagation paths are identified for the analyzed designs. Moreover, the required timing and characteristic conditions for the generation and the propagation of SETs through TSPC logic are abstracted. The impact of the input patterns and SET polarity (negative  $(1 \to 0 \to 1)$  or positive  $(0 \to 1 \to 0)$ ) on SET characteristics variation while propagating is fully explored. The variations in SET width for each possible input pattern and polarity are characterized for both static and TSPC logic.

- 2. Investigate the impact of re-converging and diverging paths on SET propagation (related to R1): The possibilities of SET width attenuation or broadening due to re-converging paths are investigated. Pulses may re-converge and overlap at a gate in a circuit if multiple paths exist between the particle striking node (affected node) and the re-converging gate. The SET propagation scenario which can induce Byzantine faults is identified. Byzantine faults are defined as faults presenting different symptoms (or logic interpretation) to different observers.

The transistor level analysis main results and observations in relation with these issues led to the following publications:

— C1: G. Bany Hamad, S. R. Hasan, O. Ait Mohamed, Y. Savaria, (2013) "Investigating the Impact of Input Patterns, Propagation Paths and Re-convergent Paths on

- The Propagation Induced Broadening." 14th IEEE Conference on Radiation Effects on Components and Systems (RADECS' 2013).

- **J1**: *G. Bany Hamad*, S. Rafay Hasan, O. Ait Mohamed, and Y. Savaria, (2014). "New insights into the single event transient propagation through static and TSPC logic", IEEE Transactions on Nuclear Science, vol.61, no.4, pp.1618-1627. In this thesis, this journal paper is reproduced in Chapter 4.

# 1.3.2 Modeling and Analysis of SET Propagation at Gate Level

At gate level, I proposed new solutions to abstract, model, and analyze SET propagation using formal verification methods. Following, the main ideas published proposed in this area are listed:

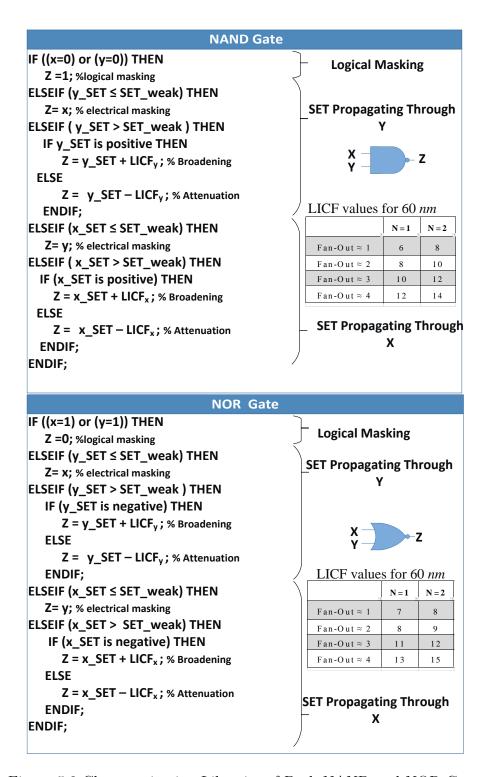

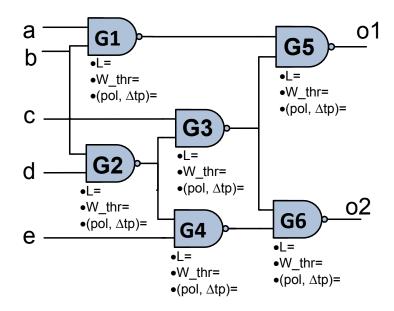

- 1. Abstraction of SET propagation behavior from transistor to gate level (related R2 and R3): In order to bridge the gap between transistor and gate levels modeling, I proposed a new logic abstraction of the SET width variation observed at the circuit level. The impact of the applied input pattern and the gate fan-out on the SET width is abstracted using the Load and Input Combination Factor (LICF). Moreover, I proposed new characterization libraries modeling SET propagation that provide a comprehensive abstraction of several propagation behaviors previously ignored at gate level. The proposed analysis and abstraction advances the state-of-the-art in modeling SET at abstraction levels higher than the circuit level, enabling more accurate estimation of the soft error sensitivity and improved reliability of digital systems. The proposed abstraction model led to the following publication:

- G. B. Hamad, S. R. Hasan, O. Ait Mohamed, Y. Savaria, "Abstracting single event transient propagation characteristics to support gate level modeling", IEEE International Symposium on Circuits and Systems (ISCAS' 2014).

- 2. Multiway decision graph based modeling and analysis of SETs (related to R3 and R4): I proposed new means of modeling SET propagation at gate level by utilizing the Multiway Decision Graphs (MDGs) [57] and transistor level characterization libraries. MDGs are chosen over other types of decision graphs because they allow defining SET width variation and other known masking effects (such as logical masking) in a single decision diagram. This analysis identifies the set of conditions, related to SET propagation and design structure, that may lead to soft errors. These conditions are abstracted as gate level characterization libraries for each design. These libraries can be used to perform SET propagation analysis at higher abstraction levels. Based on the results of this analysis, a new estimation of the design's SER is genera-

ted. This combination leads to more accurate analysis and requires less memory than contemporary techniques. The proposed MDG based modeling led to the following publications:

- G. Bany Hamad, S. Rafay Hasan, O. Ait Mohamed, and Y. Savaria, (August, 2014). "Modeling, analyzing, and abstracting single event transient propagation at gate Level", In IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), pp.515-518.

- G. Bany Hamad, S. Rafay Hasan, O. Ait Mohamed, and Y. Savaria, (2015). "Characterizing, modeling, and analyzing soft error propagation in asynchronous and synchronous digital circuits", Microelectronics Reliability, Volume 55, Issue 1, Pages 238-250.

- 3. Satisfiability modulo theories based SETs modeling and analysis (related to R3, R4, R5, and R6):

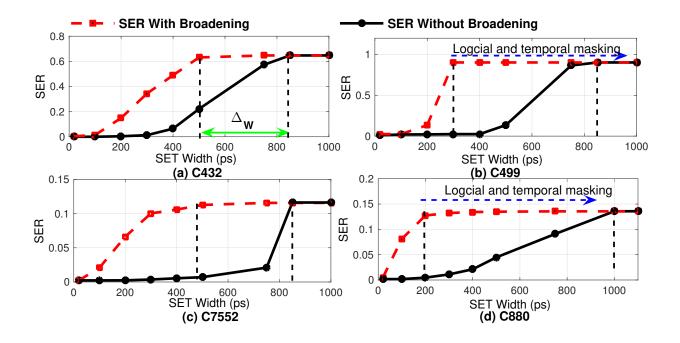

I introduced a novel methodology to evaluate the vulnerability of digital designs to SETs at gate level. This methodology provides a new technique for modeling SETs propagation by introducing awareness about the underlying observed behavior at transistor level. SET propagation is modeled as a satisfiability problem leveraging the efficiency of Satisfiability Modulo Theories (SMTs). The theories of linear integer arithmetic and difference logic are utilized to efficiently model SET width and timing constraints. Moreover, in this model, concepts of static timing analysis are adapted to compute the required timing and width for an SET to be latched. In the analysis phase, the proposed methodology computes the timing and width requirements for every vulnerable node in the design. This is done by investigating the width variation and delays along the different propagation paths. I implemented the proposed analysis on different SMT solvers in order to compare the performance of each and decide on an optimal modeling technique and solver. The solvers I used are Z3 [58], Yices [59], Mathsat [60], and CVC4 [61]. All these results are characterized into gate level propagation tables which have the following benefits: 1) They are used to measure the observability of each SET at each node and the vulnerability of the design i.e., SER. 2) They can also be used to further improve the efficiency of the analysis of soft error mitigation techniques.

The proposed SMT modeling and analysis based on SMTs led to the following publication:

— G. Bany Hamad, G. Kazma, O. Ait Mohamed, and Y. Savaria, (2016). "Comprehensive Non-Functional Analysis of Combinational Circuits Vulnerability to Single Event Transients", Forum on specification & Design Languages (FDL).

4. Layout based gate level estimation of SER due to SETs (related to R3, R4, R5, and R6):

I introduce a novel methodology to estimate the vulnerability of combinational designs to soft errors at gate level. This methodology starts with the synthesis of an RTL design into its gate level representation and then the layout of the design is extracted. Next, gates parasitics are extracted and gates timing details are characterized from the layout. These parameters are then employed to model and analyze SET propagation. A new model for SETs propagation is proposed, which captures the variations in the SET characteristics while propagating, such as the SET width attenuation and broadening. Moreover, this model includes the impact of all masking effects (logical, electrical, and temporal) and re-converging paths on SET propagation. Furthermore, a new formalism modeling SET propagation into a Satisfiability problem utilizing SMTs to utilize the design timing extracted from the layout is proposed. A new estimate of the design SER is computed.

The proposed post-layout modeling and analysis based on SMTs led to the following publications:

— G. Bany Hamad, G. Kazma, O. Ait Mohamed, and Y. Savaria, (2016). "Efficient and Accurate Analysis of Single Event Transients Propagation Using SMT-Based Techniques", IEEE International Conference on Computer-Aided Design (ICCAD).

### 1.3.3 Modeling and Analysis of SET Propagation At Register Transfer Level

I proposed different methods to model and analyze SET propagation at RTL using formal verification methods. This work is distinct in the following ways:

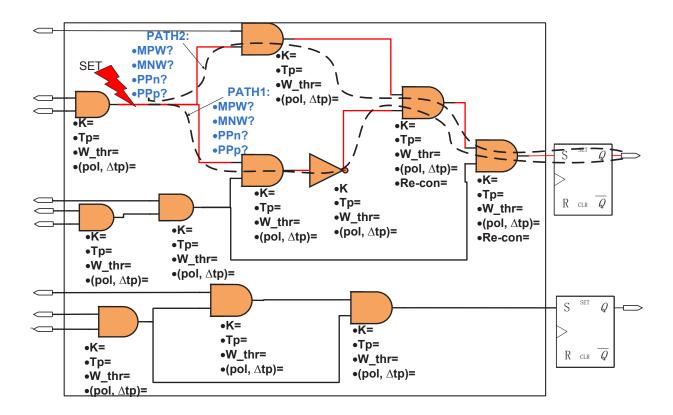

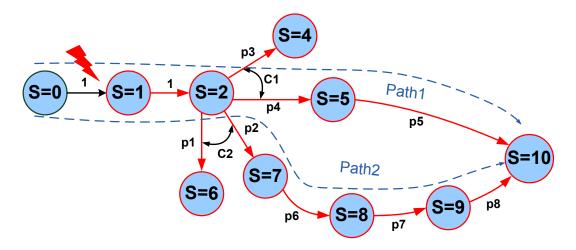

1. MDG based abstraction, modeling, and analysis of SET propagtion at RTL (related R3, R4, R5, and R6): Abstraction is one of the most relevant techniques for addressing the state explosion problem [62]. I proposed a new abstraction approach in which the components in the RTL design are modeled based on their mode of operations. An RTL component can have three modes of operation; Injection, Propagation, or Error-Free. For each injection scenario, SET propagation at RTL is modeled based on the sub-components mode of operation and their gate level characterization libraries developed beforehand. Similar to the gate level analysis, I utilized MDGs [57] to analyze SET propagation at RTL. The invariant checking tool from the MDG formal verification tool set [57] is adapted to perform this analysis. The results, which are SET propagation conditions for all injection scenarios, are reported as RTL characterization libraries.

The results of this analysis have been reported in the following publications:

- G. Bany Hamad, O. Ait Mohamed, and Y. Savaria, (May, 2016). "Towards Formal Abstraction, Modeling, and Analysis of Single Event Transients at RTL", IEEE International Symposium on Circuits and Systems (ISCAS).

- 2. Probabilistic modeling and analysis of SET propagation at RTL (related to R3, R4, R5, and R6): I proposed an efficient probabilistic reduction and modeling techniques to analyze SET propagation. I proposed two efficient reduction methods namely the Cone Of Influence (COI) and the component mode of operation methods. At RTL, SET propagation is modeled based on the proposed fault space mapping technique. The propagation of high level faults for each sub-component is modeled as Probabilistic Automata (PA) based on the propagation probabilities of low level faults reported in the pre-characterized sub-component propagation table. The PAs of all sub-components are modeled as Markov Decision Processes (MDPs). Thereafter, SET propagation is quantitatively analyzed using the proposed formal probabilistic verification technique that utilize the power of PMC. The results of this analysis are the SET propagation probabilities for all vulnerable nodes. Finally, theses probabilities are utilized to estimate SERs.

The results of this analysis have been reported in the following publications:

- G. Bany Hamad, O. Ait Mohamed, and Y. Savaria, (2014). "Probabilistic model checking of single event transient propagation at RTL level", IEEE International Conference on Electronics Circuits and Systems (ICECS), Marseille, France, pp. 451-454.

- G. Bany Hamad, O. Ait Mohamed, and Y. Savaria, (July, 2015). "Efficient Multilevel Formal Modeling, Analysis, and Estimation of Design Vulnerability to Soft Error", IEEE International On-Line Testing Symposium (IOLTS), Athena Pallas Village, Greece, pp. 1-6.

- G. Bany Hamad, O. Ait Mohamed, and Y. Savaria, (2016). "Comprehensive Multilevel Probabilistic Analysis of Single Event Transients Propagation Induced Soft Errors" Submitted for publication.

#### 1.4 Thesis Organization

The organization of this thesis is as follows.

In Chapter 3, the main sources of single event transients in digital circuits are discussed. Then, the different formal verification methods which we utilized in this thesis to model and analyze SET propagation at high abstraction levels are introduced.

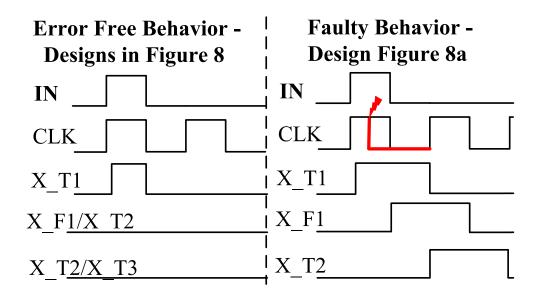

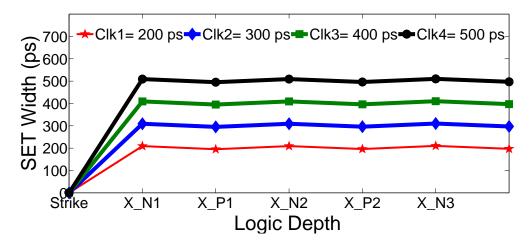

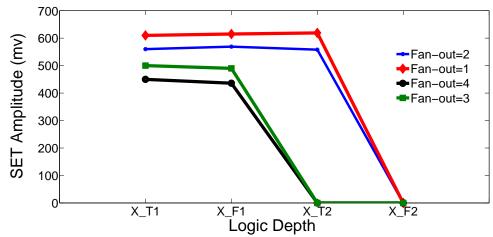

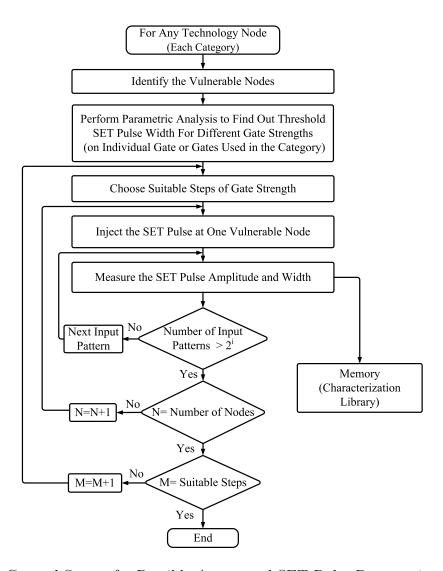

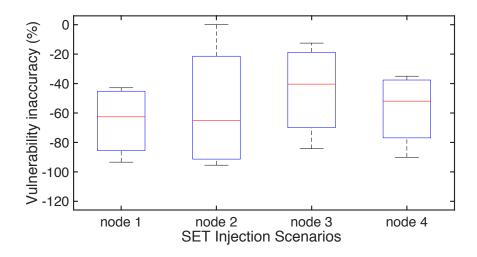

In Chapter 2, the details of the most relevant SETs modeling and analysis techniques at different abstraction levels from register transfer to post silicon levels are discussed.