Modeling and Verification of AMS Designs in Presence of Nonidealities

Ibtissem Seghaier,

Mohammed Zaki Hussein and

Sofiene Tahar

Contact:

seghaier@encs.concordia.ca

Analog and Mixed Signals circuits verification is a serious bottleneck in the design flow of modern electronic systems. This is mainly due to fundamental differences of their analog and digital

components operating modes, the continuous shrinking of circuit sizes, and their sensitivity to initial conditions uncertainties and non-idealities (namely, process variation, device jitter and noise).

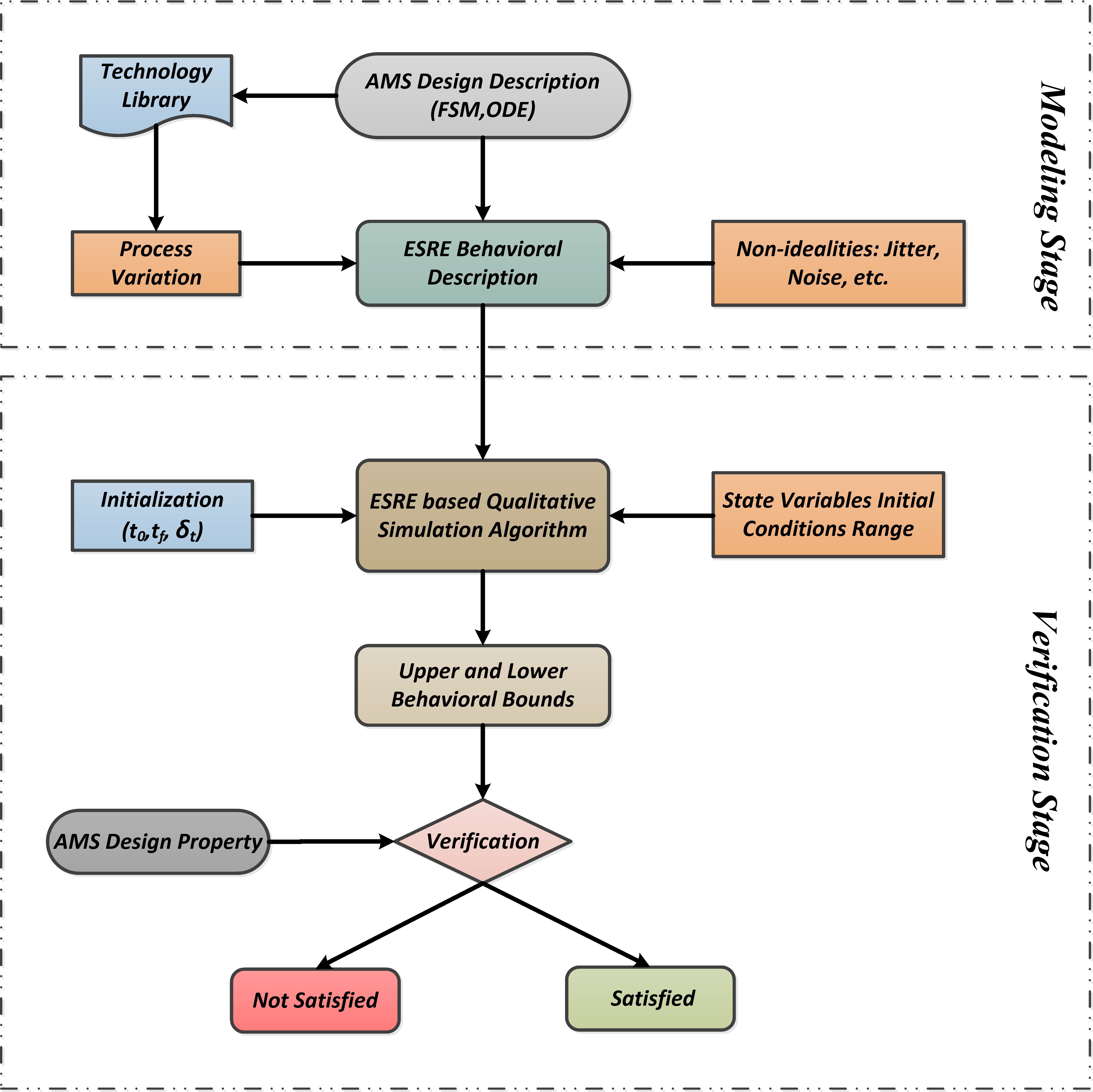

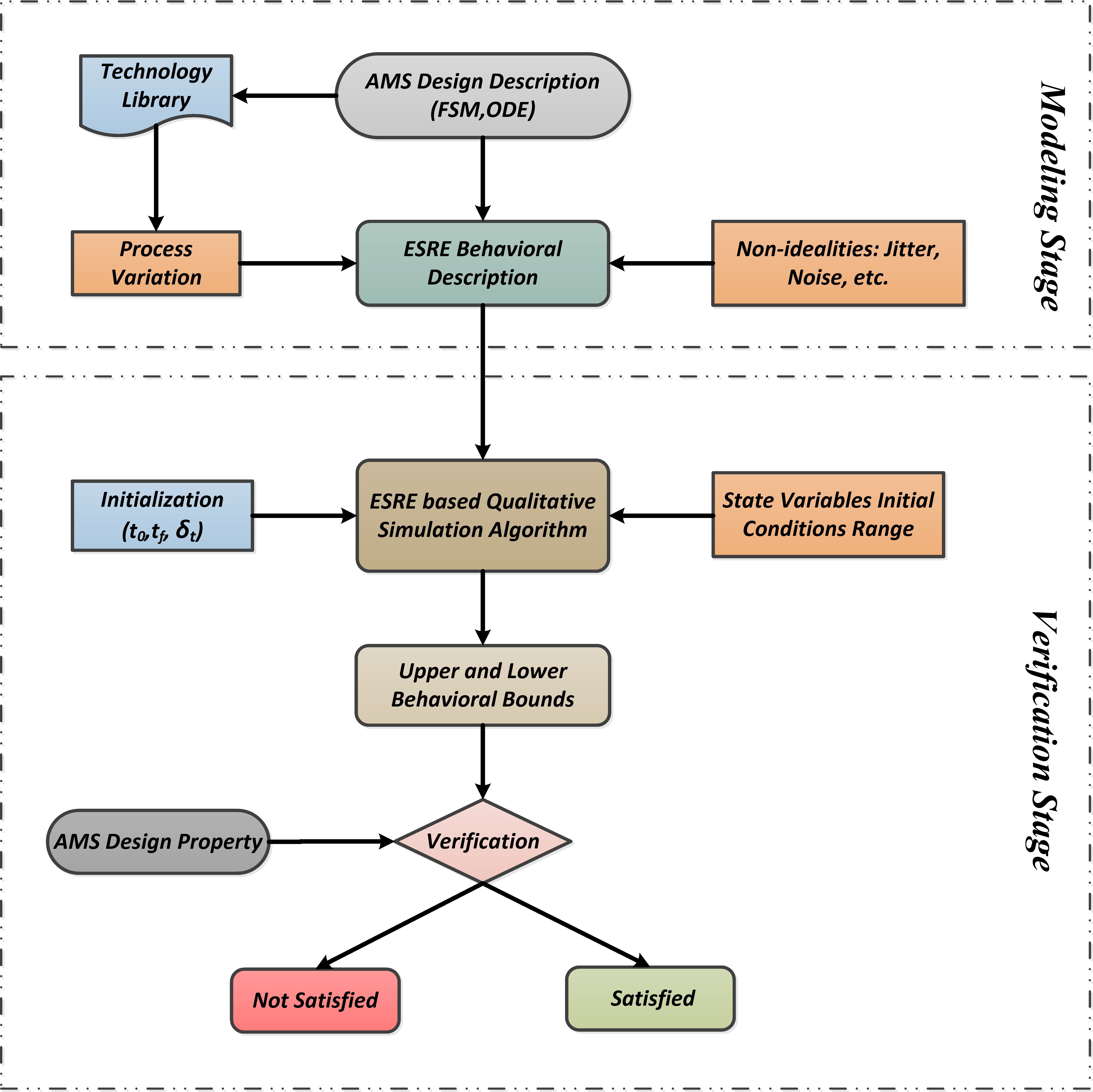

In this research, we developed a new modeling and verification methodology of AMS designs in presence of jitter and process variation using qualitative simulation.

Our proposed methodology is depicted in the above figure. In the modeling stage, an Extended System of Recurrence Equations (ESREs) model that interleaves the analog and digital parts of the circuit is created. To accommodate the imprecise nature of AMS circuits, non-idealities will be

considered and integrated in the ESRES. In the sequel, a modified qualitative simulation algorithm is conducted to guarantee that an AMS design property is sound for every possible initial condition and parameter values.

We illustrated the efficiency of the proposed methodology on modeling a 3rd. order Phase Locked Loop and verifying its locking time.

[1] I. Seghaier, H. Aridhi, M. H. Zaki, and S. Tahar, A Qualitative Simulation Approach for Verifying PLL Locking Property [Proc. Great Lakes Symposium on VLSI (GLSVLSI'14), Houston, Texas, USA, May 2014, pp. 317-322.]